运用 Altium Designer 进行 PCB 电路的绘制与仿真

Altium公司最早推出的电子设计自动化(EDA,Electronics Design Automation)产品名为Protel,在经过一系列的企业并购与技术整合之后,于 2009 年更名为Altium Designer 09,紧接着又于 2012 年推出Altium Designer 13.0,本文将要介绍的Altium Designer 17.1则是 Altium 公司于 2017 年发布的产品,可用于设计板级原理图并进行 PCB 布线,同时整合了 SPICE 仿真以及 FPGA 设计等高级功能。

经过多年的迭代与发展,Altium Desinger

已经不再只局限于作为一款 EDA

工具,其功能已经贯穿于电子设计的全流程,包括 MCU 微控制器与 FPGA

设计建模、电路 SPICE 仿真验证、元器件库封装、电路原理图绘制、PCB

版图绘制、PCB 信号完整性验证、PCB 制板文件生成等功能,本文主要围绕

Altium Desinger 的

原理图与 PCB 绘制、元器件封装、PCB 仿真与验证

三个核心功能进行讲解。

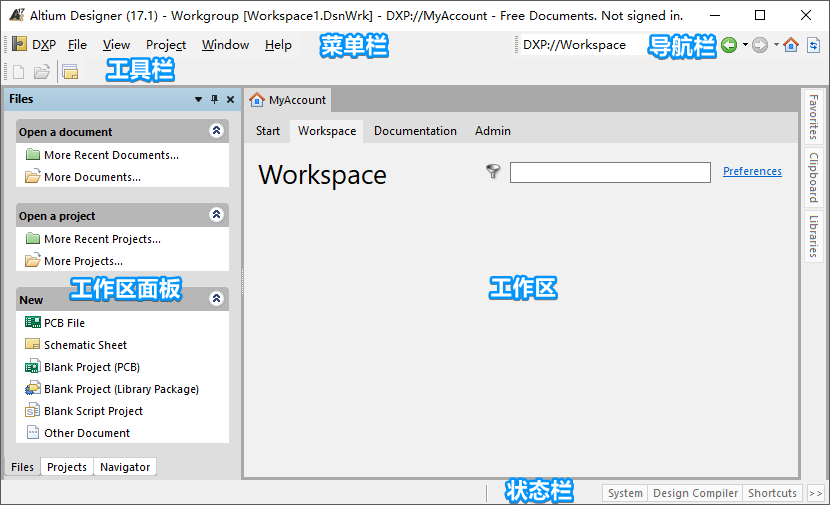

概览与设置

Altium Designer 17 的主界面要分为菜单栏、工具栏、导航栏、工作区面板、工作区、状态栏等几个部分,其中工具栏、菜单栏会跟随用户编辑器环境的变化而变化,下图标注了主界面的各个组成部分:

系统设置

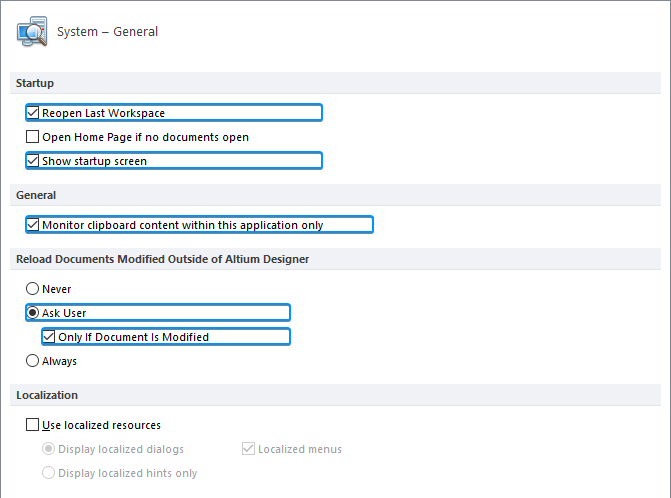

为了更加高效的运用 Altium Designer,需要进行一系列的初始化工作,点击菜单栏 DXP -> Preferences -> System -> General 进行如下设置:

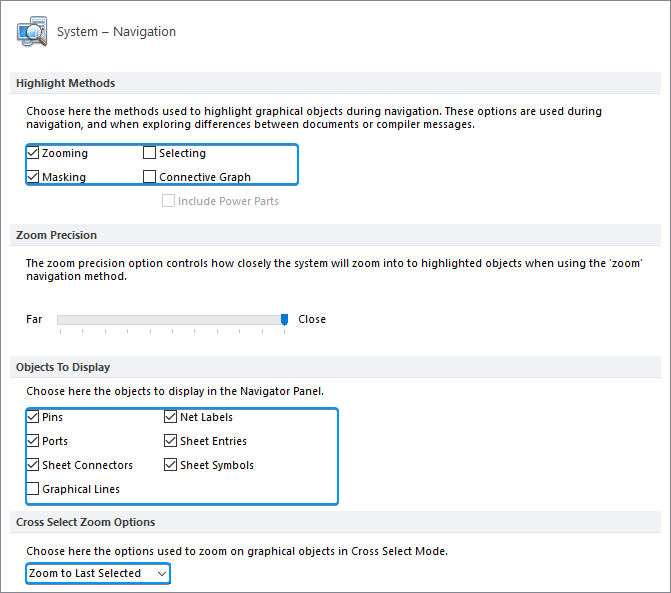

在执行操作导航过程当中,为了更加快速的定位所选择的对象,需要将所选对象进行高亮与放大处理,即交叉选择模式(Cross Select Mode),点击 DXP -> Preferences -> System -> Navigation 进行如下设置:

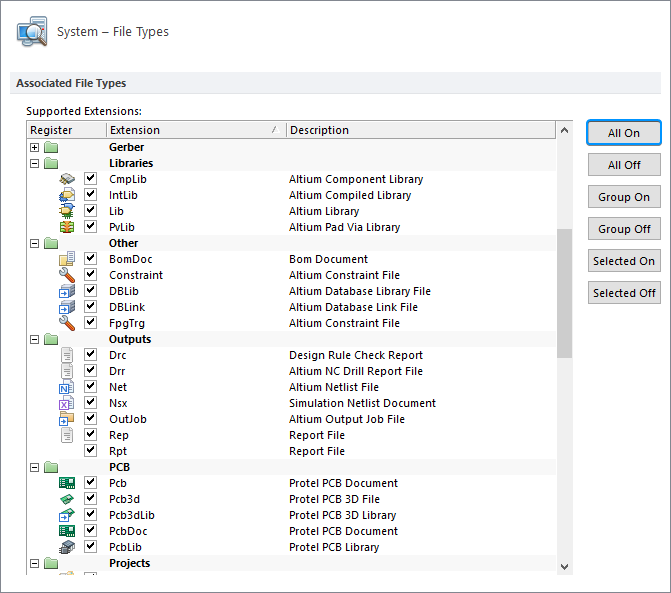

设置文件关联选项,点击 DXP -> Preferences -> System -> File Types 进行勾选:

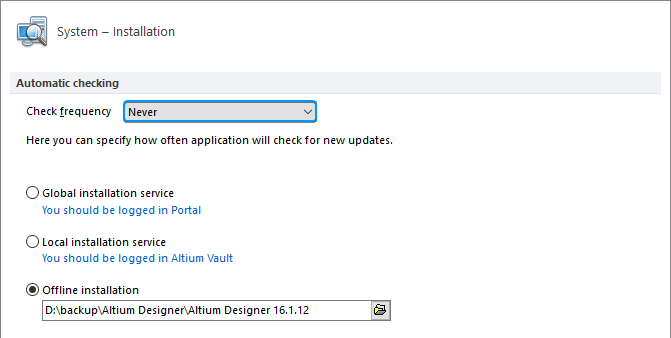

关闭自动更新检查,通过 DXP -> Preferences -> System -> Installation 进行如下设置:

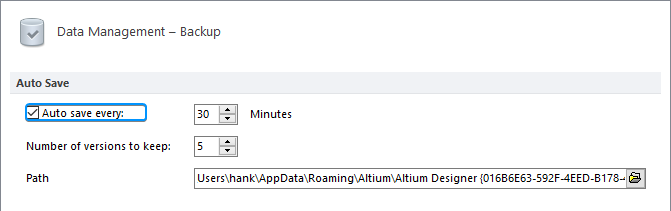

文件自动备份设置,选择 DXP -> Data Management -> Backup 进行如下设置:

原理图设置

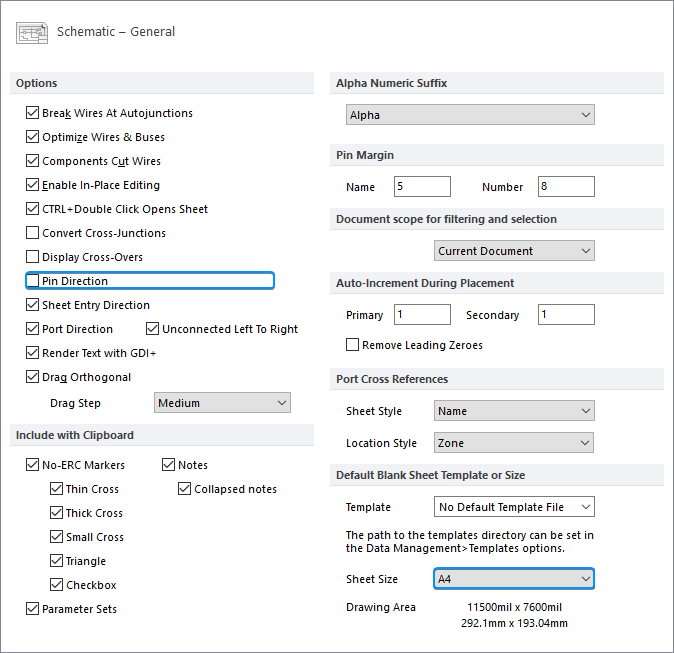

打开 DXP -> Schematic -> General

并且取消勾选Pin Direction选项,并且设置空白原理图模板为

A4 尺寸:

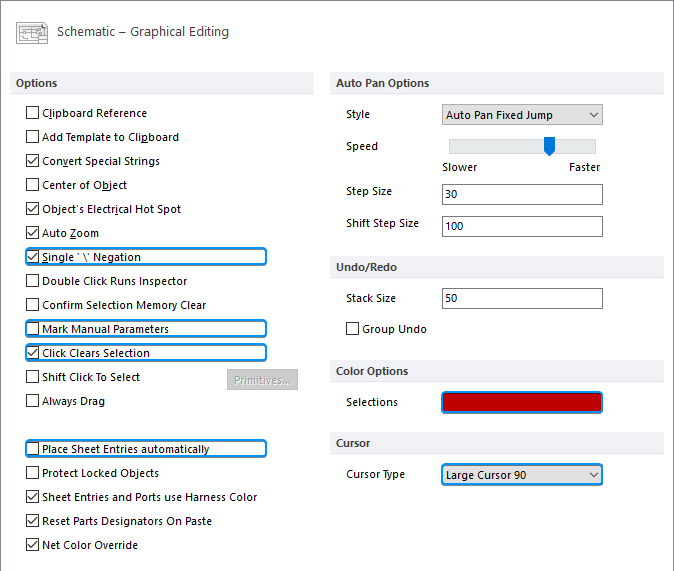

打开 DXP -> Schematic -> Graphical

Editing,选择选项Single'\'Negation表示网络标号上使用\符号表示负信号,从而使网络标号出现上划线。选择选项Click Clears Selection表示单击空白处退出选择状态,便于多选环境下退出选择状态。选择选项Color Option表示所选中对象上的虚线框颜色。选择选项Cursor表示原理图编辑界面内的鼠标形状,这里修改为Large Cursor 90表示全屏十字指针。最后,取消Mark Manual Parameters与Place Sheet Entries automatically两个选项的默认勾选。

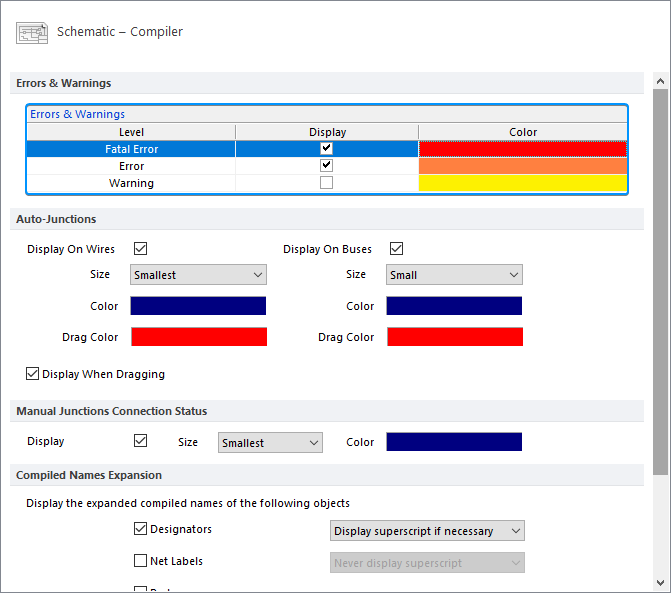

将 DXP -> Schematic -> Compiler 下面的

Errors & Warnings 里

Fatal Error的颜色设置为红色:

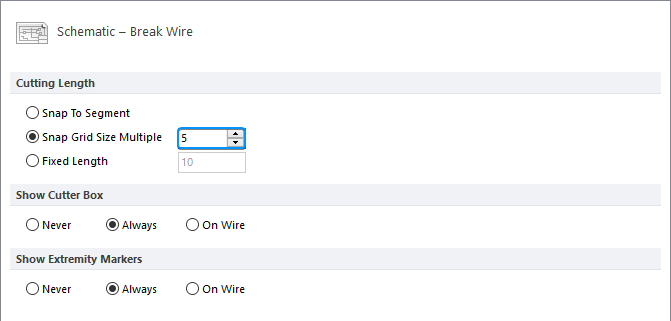

进入 DXP -> Schematic -> Break Wire 设置

Altium Designer

的导线切割功能(即将连接的导线断开),切割宽度通常取值为线宽的

5 倍:

PCB 设置

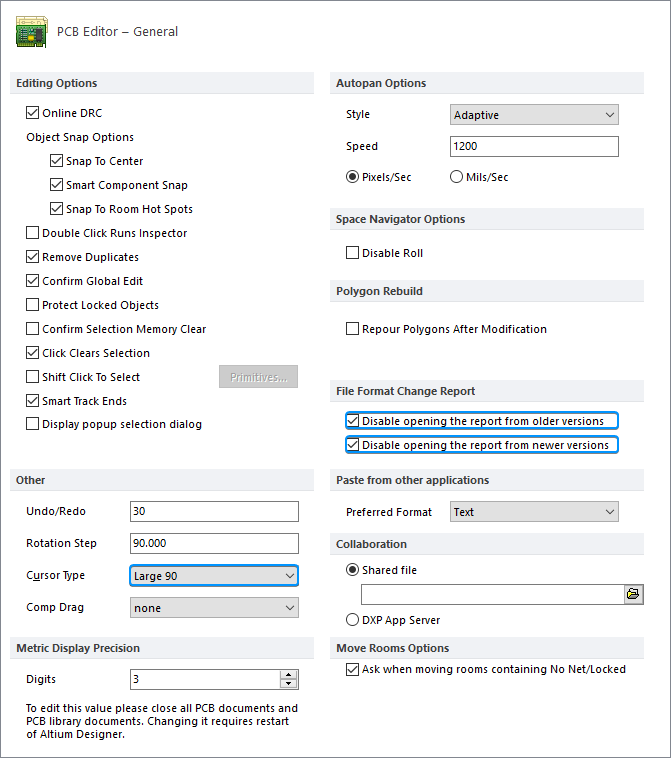

打开 DXP -> PCB Editor -> General

进行设置,选择Cursor Type为更加便于布局布线对齐的Large 90风格,并且取消File Format Change Report下的两个选项,避免

HTML 文档打扰。

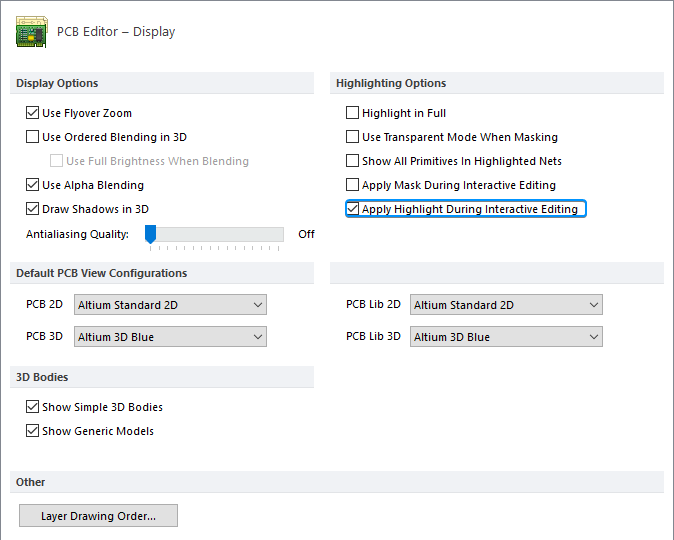

勾选 DXP -> PCB Editor -> Display

里Highlighting Options下的走线时使用高亮模式Apply Highlight During Interactive Editing。

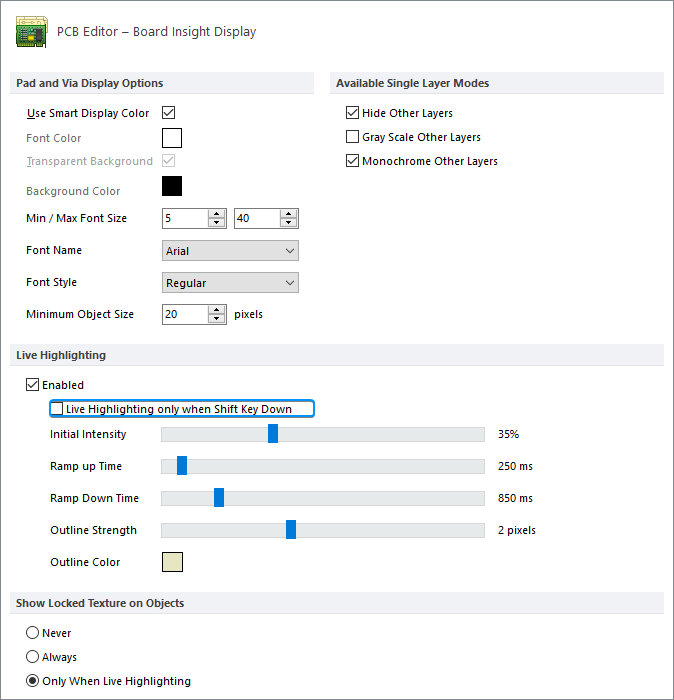

取消 DXP -> PCB Editor -> Board Insight

Display 下

Live Highlighting only when Shift Key Down 的勾选:

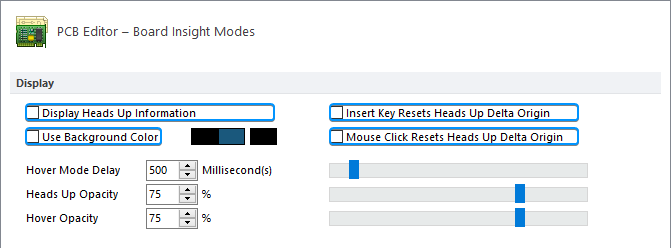

取消 DXP -> PCB Editor -> Board Insight Modes 里如下几个选项的勾选,当然也可以在编辑 PCB 文件时使用【Shift + H】快捷键关闭。

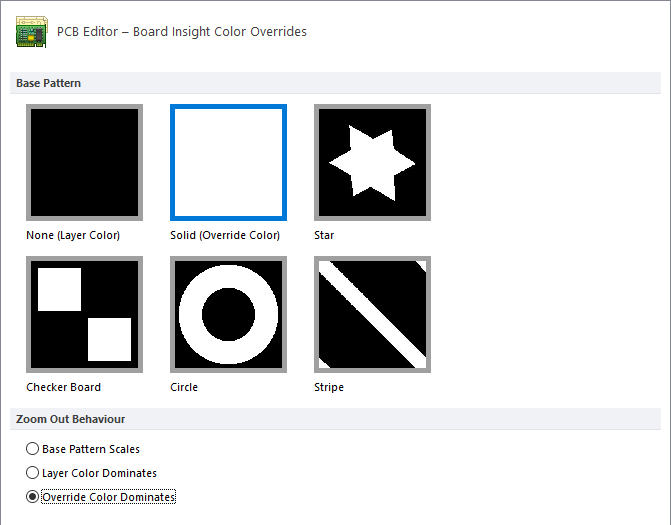

点击选择 DXP -> PCB Editor -> Board Insight Color

Overrides

下Base Pattern里的Solid (Override Color),防止颜色过于杂乱造成眩晕。

同理,DXP -> PCB Editor -> DRC Violations

Display

下的Violation Overlay Style也同样选择Solid (Override Color)。

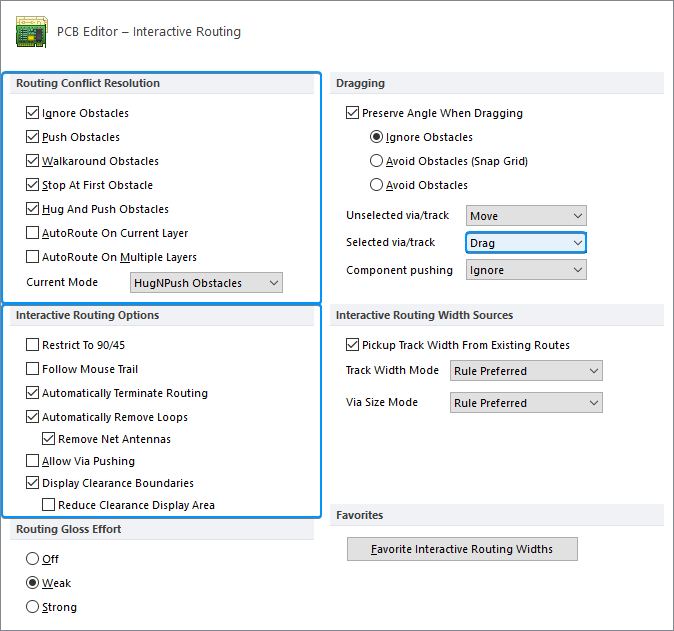

打开 DXP -> PCB Editor -> Interactive Routing 进行走线相关的设置:

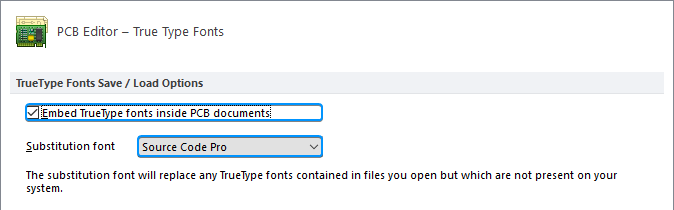

取消勾选 DXP -> PCB Editor -> True Type Fonts

下的嵌入字体到 PCB

文档Embed TrueType fonts inside PCB documents选项,可以有效的减小所输出文件的尺寸:

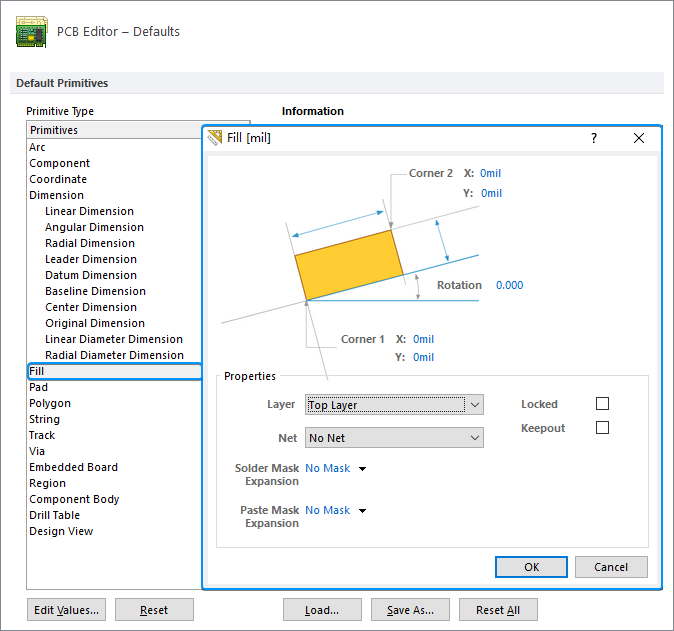

选择 DXP -> PCB Editor -> Default 可以设置 PCB 编辑器中的元素参数的默认值:

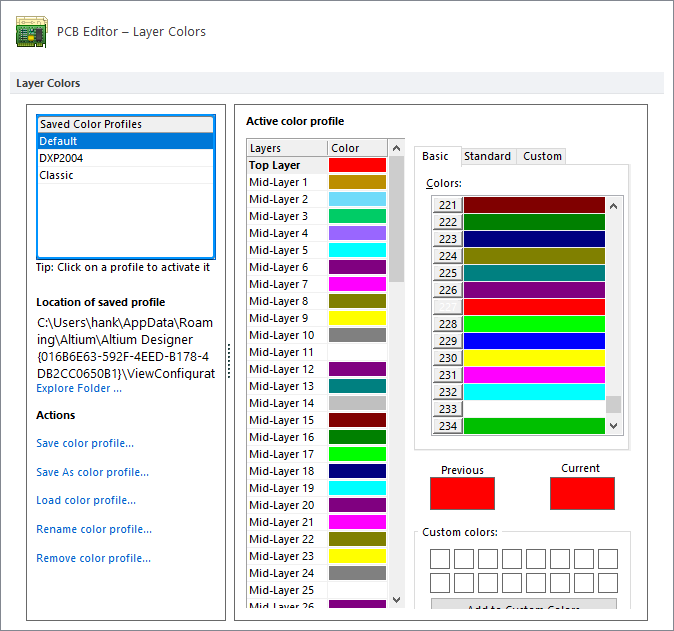

选择 DXP -> PCB Editor -> Layer Colors 可以对 PCB 的每一层颜色进行单独设置:

点击 Preferences 上的【Save】按钮,可以将上述的配置保存为以

.DXPPrf作为后缀名的文件。

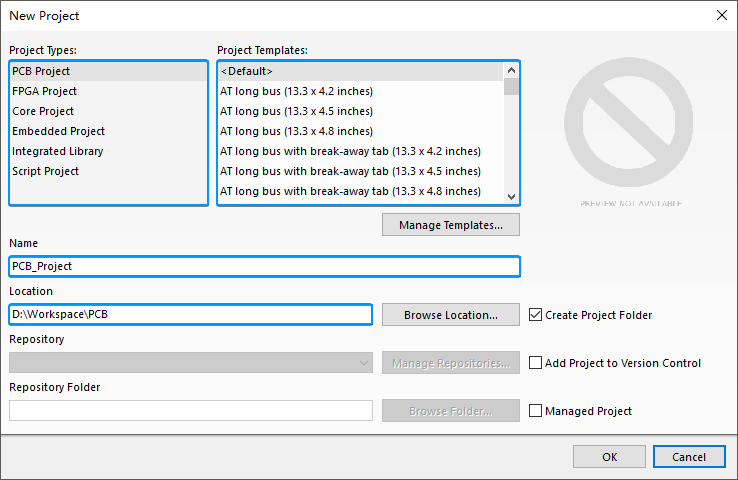

工程创建

工程 Project 是 Altium Designer

当中各种类型源文件相互关联的集合体,一个完整的 Altium Designer

工程至少应该包括.PrjPcb工程文件、.SchLib元件库文件、.SchDoc原理图文件、PcbLib

PCB 库文件、PcbDocPCB

文件、.NET网络列表文件。

执行菜单栏上的 File-New-Project...按照下图格式新建一个工程:

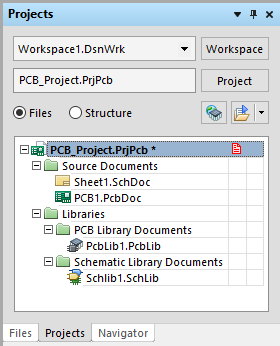

工程建立以后,会在 PCB

工作目录下建立一个名为PCB_Project的工程文件夹,最终形成的目录结构如下所示:

1 | D:\Workspace\PCB |

接下来执行如下一系列的操作,建立原理图与 PCB 文件,以及相关的库文件:

- 执行菜单命令 File -> New -> Schematic

或者在工程名上单击鼠标右键 Add New to Project ->

Schematic 创建原理图

Sheet1.SchDoc; - 执行菜单命令 File -> New -> PCB

或者在工程名上单击鼠标右键 Add New to Project -> PCB

创建 PCB 文件

PCB1.PcbDoc; - 执行菜单命令 File -> New -> Library -> Schematic

Library 或者在工程名上单击鼠标右键 Add New to Project

-> Schematic Library

创建元件库

Schlib1.SchLib; - 执行菜单命令 File -> New -> Library -> PCB

Library 或者在工程名上单击鼠标右键 Add New to Project

-> PCB Library 创建 PCB 库

PcbLib1.PcbLib;

上述文件新建完成以后,最终形成的项目目录结构如下图所示:

最终,计算机磁盘上实际形成的文件夹目录结构如下所示:

1 | D:\Workspace\PCB |

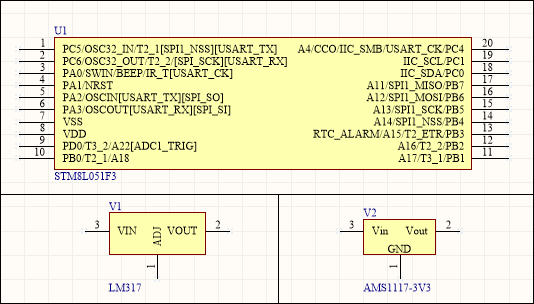

原理图元件库

元件符号是电子元件在原理图上的表现形式,主要由边框、引脚名称与序号、元件名称与说明组成,并且元件符号中的引脚序号与电子元件实物的管脚必须逐一对应。建立元件库时,使用频率较高的非工具栏上的【Place】下拉菜单莫属,该菜单下拥有如下命令:

| 符号 | 作用 | 符号 | 作用 |

|---|---|---|---|

|

放置线(Place Line) |

|

新建器件(Create Component) |

|

放置贝塞尔曲线(Place Bezier) |

|

添加器件部件(Add Component Part) |

|

放置椭圆弧(Place Elliptical Arcs) |

|

放置矩形(Place Rectangle) |

|

放置多边线(Place Polygons) |

|

放置圆角矩形(Place Round Rectangle) |

|

放置文本字符串(Place Text String) |

|

放置椭圆(Place Ellipses) |

|

放置超级链接(Place Hyperlink) |

|

放置图形(Place Graphic Image) |

|

放置文本框(Place Text Frame) |

|

放置引脚(Place Pin) |

此外,还可以使用工具栏上的【Place Symbol】菜单去放置一些元件符号,该下拉菜单拥有如下命令:

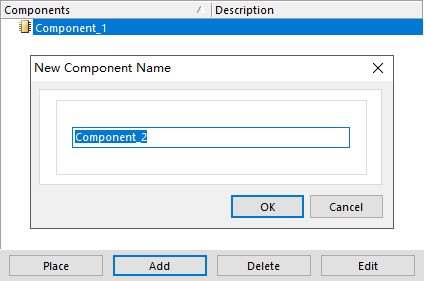

Altium Designer 左侧的工作区面板下,主要拥有如下几个较为常用的子面板,首先是元件 Components 管理子面板,主要用于管理元件的放置、添加、删除、编辑:

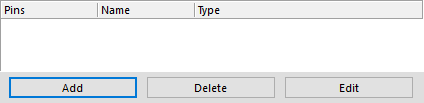

引脚 Pins 管理子面板,主要用于进行原理图上元件引脚的添加、删除、编辑:

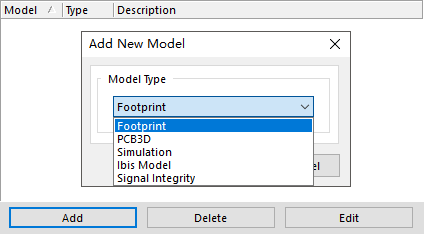

模型 Model 管理子面板,主要用于管理元件的封装、3D、仿真等模型:

新建元件

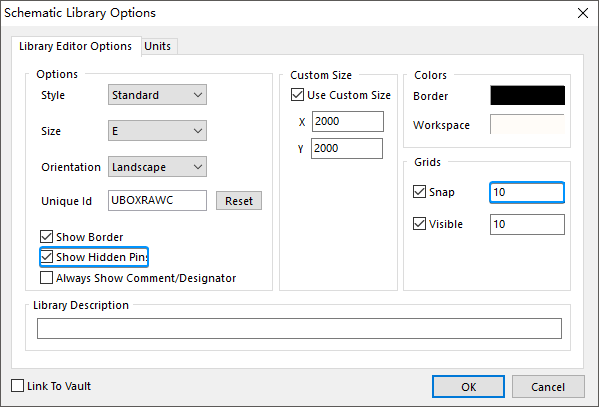

点击菜单命令 Tools -> Document Options...,进入元件库编辑器工作区选项编辑窗口,然后执行下图所示的操作:

单击 Components

子面板上的【Add】按钮,可以添加一个新的元件,然后也可以通过菜单栏上的

Tools -> Rename Component

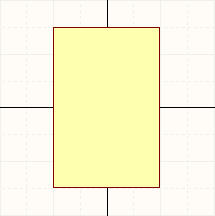

重命名这个元件,一般以电子元件的型号作为元件的命名,下面新建了一个元件Component_1,并且放置了一个矩形框:

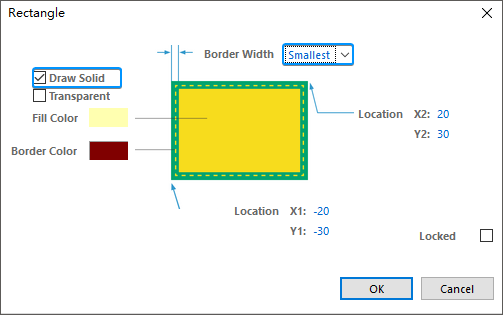

双击该矩形框,可以调整其属性,例如选择是否使用填充以及调整边框宽度:

单击绘制工具栏当中的快捷按钮【Place

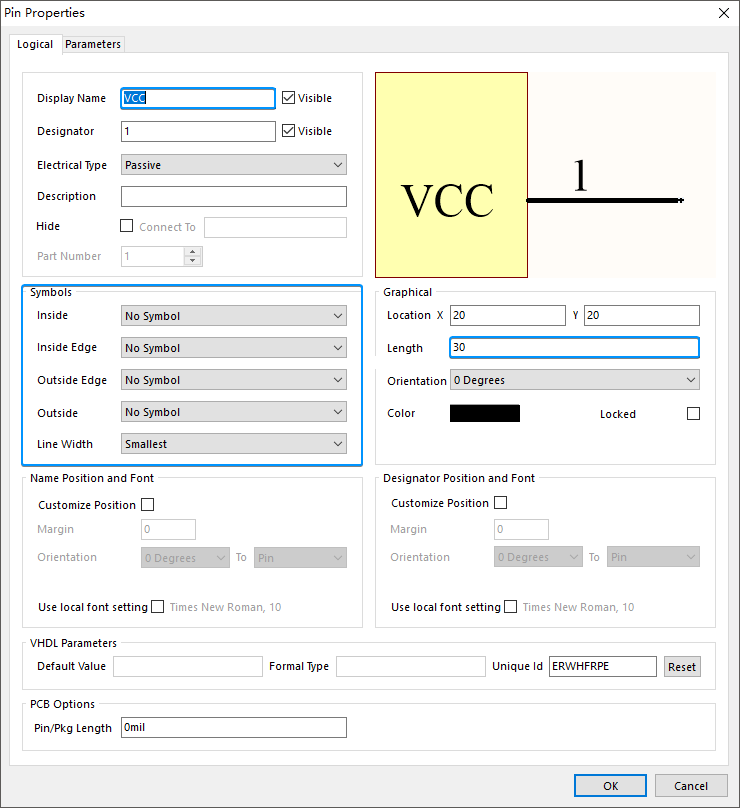

Pin】,放置管脚时要注意将具有电气特性(标识x)的一端朝外(通过空格键调整),以用于后续原理图绘制时的走线连接。放置过程中按下【Tab】键或者放置完毕后双击,可以设置管脚的属性:

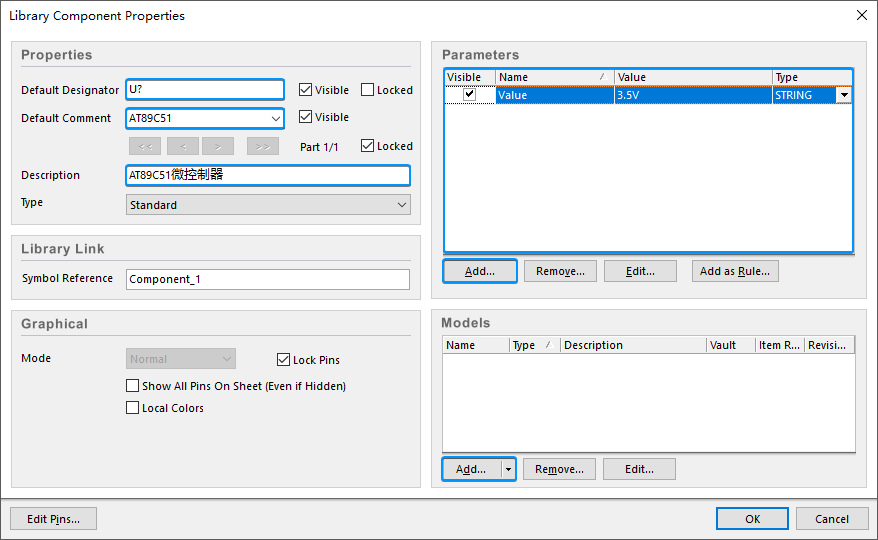

完成上述步骤以后,图形元素就绘制完毕了,此时需要设置这个绘制好的元件属性,在元件库面板列表中选中该元件,执行菜单栏命令 Tools -> Component Properties... 打开元件属性设置对话框,或者在元件库面板中双击该元件名称也可以打开该对话框:

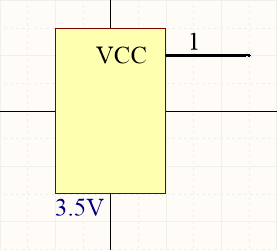

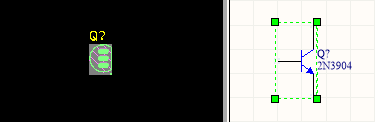

保存上述配置之后,最终得到的元件效果如下图所示:

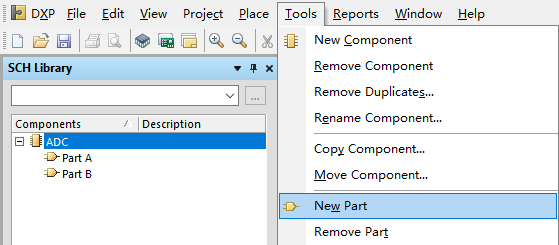

如果一个元件封装包含有多个相对独立的功能部件时,就可以采用多部件元件。这里首先创建一个名为ADC的元件,在

Components 子面板的列表中选中该元件,然后点击菜单

Tools -> New Part,此时会生成 2

个部件Part A和Part B

注意:需要设置多部件元件属性,可以通过双击该多部件元件进行设置,毋须对单个部件进行设置。

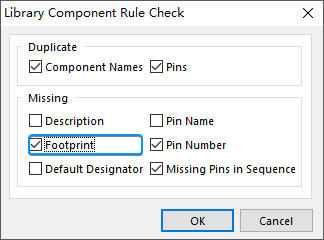

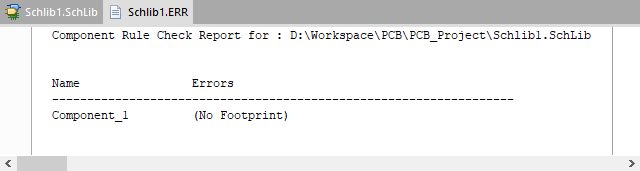

元件规则检查

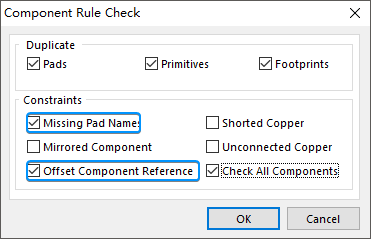

如果想要检查自定义的元件是否符合规范,或者需要了解该元件的一些信息,可以通过元件的检查与报告功能来实现。首先打开元件库面板 SCH Library,选中元件库当中需要进行检查的元件,选择菜单栏的命令 Reports -> Component Rule Check... 打开库组件规则检查对话框,然后勾选当前需要进行检查的条目:

最后,点击【OK】就会自动打开并且弹出检查结果文件Schlib1.ERR,:

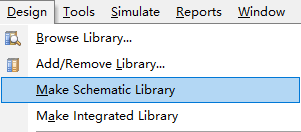

生成元件库

打开需要导出元件库的原理图,点击 Altium Designer 菜单栏的

Design -> Make Schematic

Library,即可将当前原理所使用的元件库输出为一个以.SCHLIB作为后缀名的库文件。

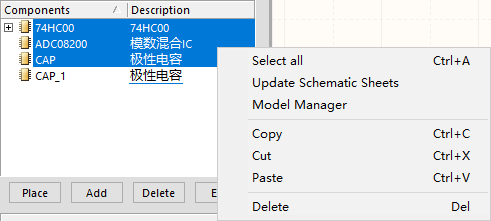

元件库复制

打开需要复制的元件库文件,单击选择或者按住【Shift】键多选等待复制的元件,然后鼠标右键选择【Copy】,然后打开目标元件库,鼠标右键执行【Paste】命令,即可以跨库完成元件的复制。

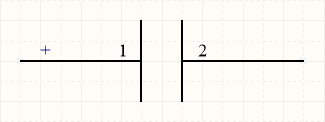

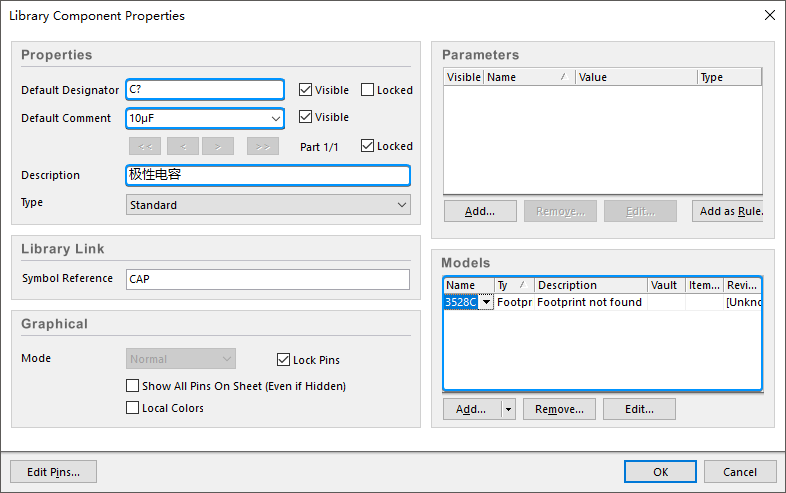

实例:创建电容

- 单击 Components 子面板上的【Add】按钮,添加一个名为 CAP 的电容元件;

- 执行菜单命令【Place

Line】,放置两条线代表电容的两极;执行菜单命令【Place

Pin】,并在放置状态按下【Tab】键设置属性,管脚的名称和序号统一为数字

1和2; - 由于电容的管脚不需要进行信号识别,可以双击管脚设置其属性,取消勾选

Display Name的Visible选项,避免显示的名称和标识符过多而造成视觉干扰; - 分别采用菜单命令 Place Line 以及 Place Text

String 绘制电容的管脚及其极性标识

+。 - 双击 Components 子面板上的电容名称

CAP 设置该元件的属性,这里将

标志符(Designator,[,dɛzɪg'netɚ])设置为

C?,将 Comment 填写为10μF,Description 填写为极性电容,然后在 Models 添加名称为3528C的 Footprint,从而最终完成了电容元件的创建。

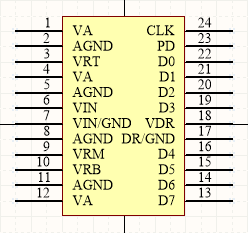

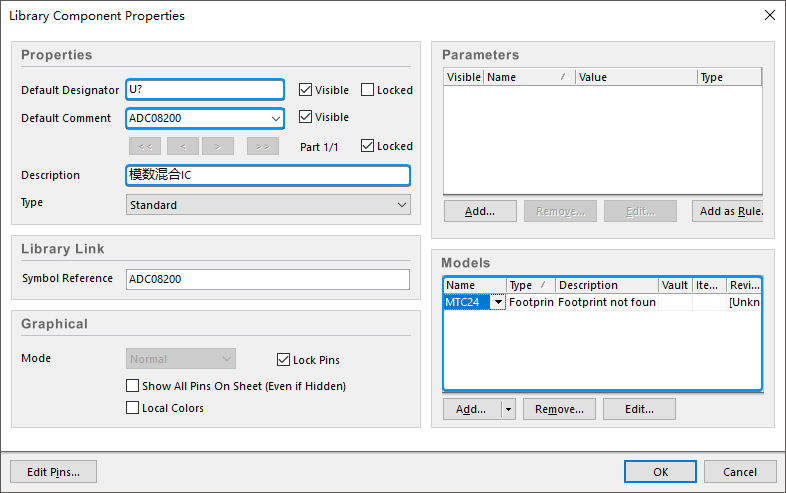

实例:创建 ADC

- 执行菜单命令Tools -> New

Component,新建一个名称为

ADC08200的集成电路元件; - 单击工具栏上的快捷按钮【Place Rectangle】,绘制一个空白的矩形框;

- 单击【Place

Pin】,在放置状态按下【Tab】键,分别按照下图所示设置管脚的名称和序号,且管脚长度默认为

30; - 随机放置好管脚以后,使用 Altium Designer 提供的对齐操作命令进行快速对齐;

- 双击元件设置其属性,Designator

设置为

U?,Comment 填写ADC08200,Description 填写为模数混合IC,在 Models 添加名称为MTC24的封装,即完成该元件的创建。

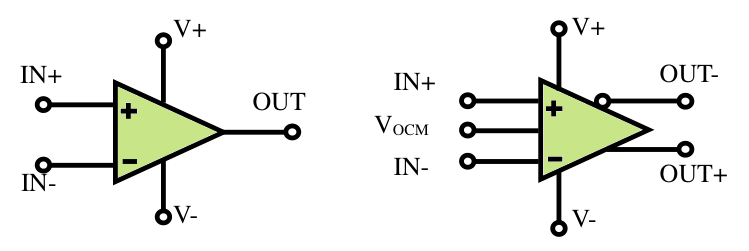

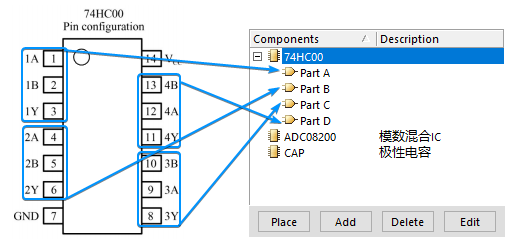

实例:创建放大器

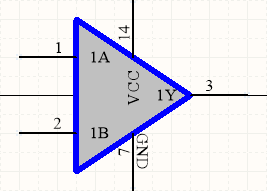

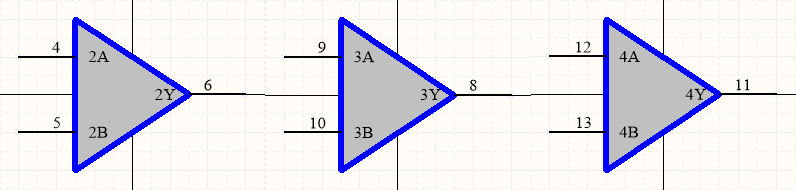

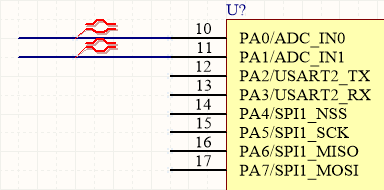

任何元件原则上都可以被划分为多个子部件,这里将 74HC00 放大芯片的 4 个独立功能与非门,分别创建为相应的子部件:

- 点击 Tools -> New Component

新建一个名为

74HC00的元件; - 通过放置多边形 Place Polygons

拖拽一个三角形,并且保存为

Part A,公用的VCC和GND管脚亦放置在该子部件;

- 接着执行 Tools -> New

Part,分别创建

Part B、Part C、Part D子部件,并且分别设置相应的属性;

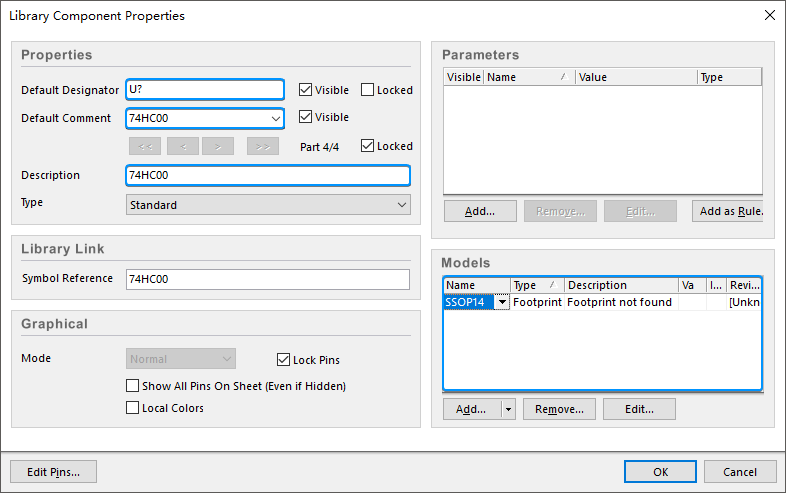

- 双击元件设置属性,Designator

设置为

U?,Comment 填写74HC00,Models 添加名称为SSOP14的封装,最终完成该多子部件元件的创建。

原理图绘制

原理图用于表示当前电路当中电子元件之间的连接关系,由原理图可以推导出如何进行 PCB Layout(布线)。点击 Altium Designer 菜单栏 File -> New Schematic 创建原理图,当 Altium Designer 处在原理图编辑器界面时,工具上的主要图标如下所示:

![]()

下面表格对于工具栏上的每个图标所对应的功能与快捷键进行了说明:

| 符号 | 作用 | 符号 | 作用 |

|---|---|---|---|

放置线(Place Wire) |

放置器件图表符(Place Device Sheet Symbol) |

||

放置总线(Place Bus) |

放置线束连接器(Place Harness Connector) |

||

放置信号线束(Place Signal Harness) |

放置线束入口(Place Harness Entry) |

||

放置总线入口(Place Bus Entry) |

放置端口(Place Port) |

||

放置网络标号(Place Net Label) |

Place Non-Specific No ERC |

||

GND

电源端口(GND Power Port) |

Place No ERC Targeting a Specific Error |

||

VCC

电源端口(VCC Power Port) |

网络颜色(Net Colors) |

||

放置器件(Place Part) |

放置 C

代码符号(Place C Code Symbol) |

||

放置图表符(Place Sheet Symbol) |

放置 C 代码入口

(Place C Code Entry) |

||

放置图纸入口(Place Sheet Entry) |

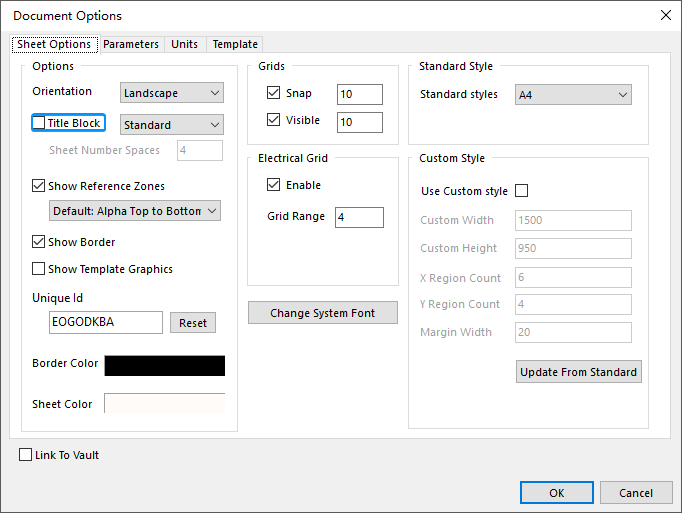

原理图设置

执行菜单栏命令 Design -> Document Options... 或者双击原理图边框,可以进入原理图页参数设置界面,从而根据产品需要设置合适的原理图尺寸以及方向:

注意:取消

Title Block选项的勾选,可以去除原理图右下角的默认模板信息。

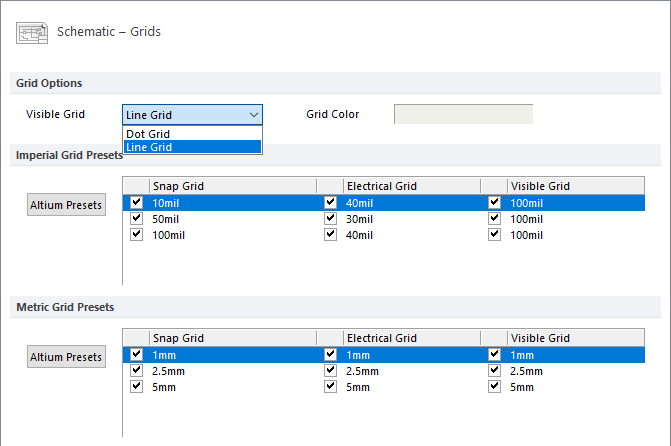

使用网格便于放置元件和绘制导线,执行 Tools -> Schematic

Preferences -> Grids

进入原理图网格设置界面,可以同时对捕获网格(Snap

Grid)、电气网格(Electrical Grid)、可视网格(Visible

Grid)的尺寸进行设置,参数取值都建议设置为5的倍数:

点击菜单栏 View -> Grids -> Toggle Visible Grid 或者快捷键 V + G + V,可以切换网格的隐藏与显示。

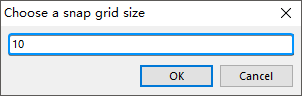

执行 View -> Grids -> Set Snap Grid...

或者使用快捷键 V + G + S 对捕获网格(Snap

Grid)进行设置,依然建议将其设置为5的整数倍,这里推荐设置为10:

注意:捕获网格的设置必须与元件库里的网格保持一致,从而保证连接导线时不会出现偏移问题。

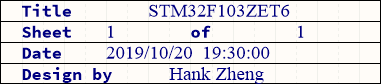

Altium Designer

提供的原理图模板包含了标题、外观属性方面的设置,方便开发人员直接调用,Altium

Designer

默认的模板保存在安装目录下的Templates文件夹。当然,开发人员也可以定义自己的模板,这里新建一张原理图并按照上面描述的方法,去除原理图右下角的默认模板信息,然后调用菜单栏上的【Place

Line】和【Place Text】绘制如下的表格和文本:

接着操作菜单栏命令 Design -> -> General Templates -> Choose Another File 选择需要显示的模板,此时会弹出模板更新提示框,要求指定模板更新的范围:

注意:如果需要放弃当前使用的模板,那么可以执行 Design -> Templates -> Remove Current Template... 移除当前所使用的模板。

元件操作

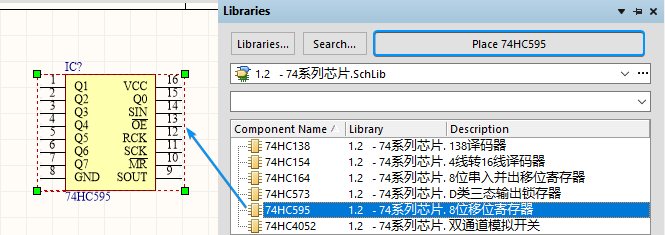

创建好元件库以后,需要将创建好的元件放置到原理图当中,正式开始电路原理图的设计工作。首先,使用快捷键

D + B 或者点击右侧 Libraries

面板导入74系列芯片.SchLib元件库。

放置元件

从上面安装的74系列芯片.SchLib元件库当中找到74HC595位移缓存器,采用双击、向原理图拖拽、点击库面板上方的【Place

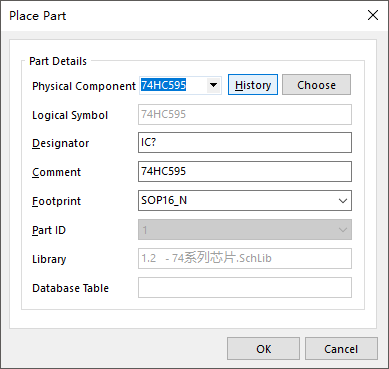

74HC595】,将该元件放置到新建的原理图上:

此时,点击菜单栏上的 Place -> Part... 或者按下快捷键 ** P + P **,会弹出一个元件放置对话框,如果需要再次放置,单击【OK】按钮即可:

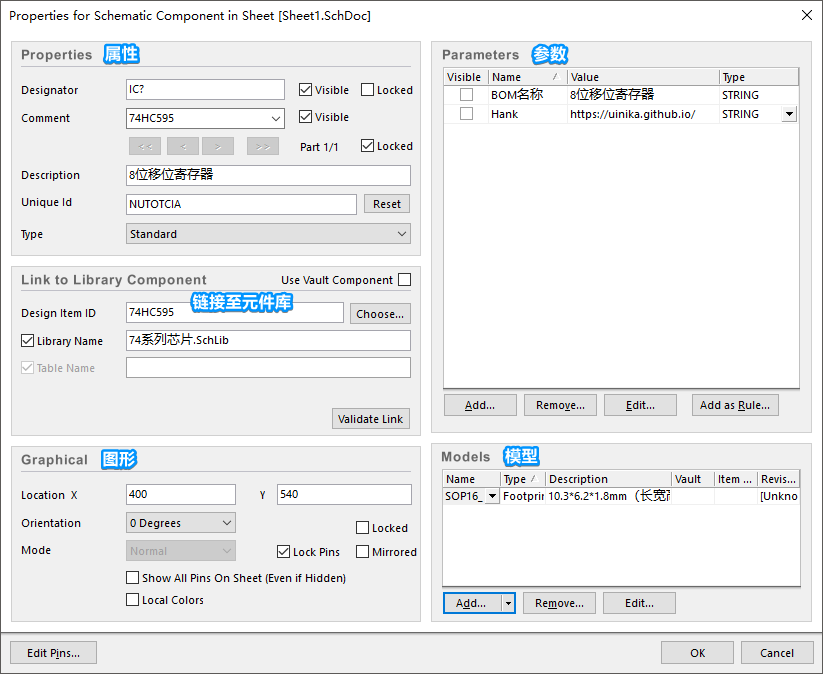

原理图上的每个元件都拥有自己的属性,Altium Designer 提供了 4 种打开原理图元件属性设置对话框的方法:

- 从元件库选取元件放置到原理图过程中,当光标还处于十字状态时按下【Tab】键;

- 元件放置到原理图以后,选中元件然后双击鼠标左键;

- 鼠标选中元件并且按住鼠标左键不松开,同时按下【Tab】键;

- 点击菜单上的 Edit -> Change 或者按下快捷键 E + H,此时光标会变成十字状态,将其放置到元件上单击即可。

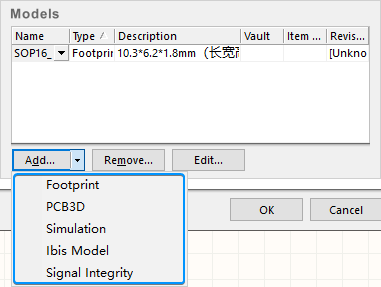

上面截图中的 【Models】

区域主要用来添加元件对应的模型,包括Footprint(PCB

封装模型,即原理图到 PCB

的映射模型)、Simulation(仿真模型)、PCB3D(PCB

上元件的 3D

模型)、Signal Integrity(信号完整性分析模型):

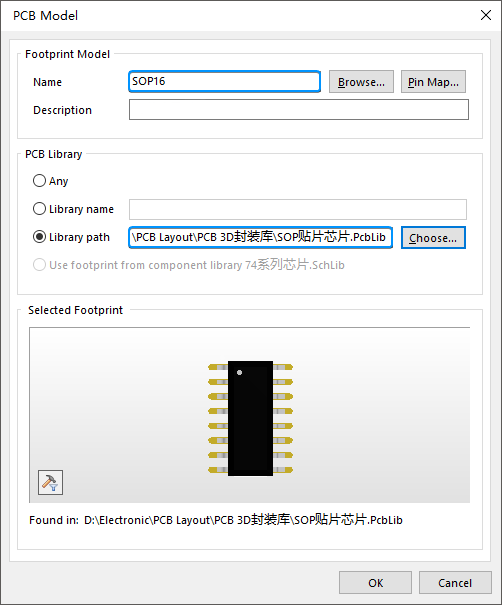

通过单击【Add…】按钮添加所需的模型,一般经常使用的是添加 PCB

封装模型,点击后弹出 PCB

模型管理界面,此处需要填写模型所在的磁盘路径(如果 PCB

封装库在本工程下,则路径设置选择【Any】,可以通过名称自动匹配;反之,则可以通过指定封装库的路径来进行匹配),当封装名称与模型匹配完成之后,Selected Footprint栏就会自动展示该封装的预览图像:

选择元件

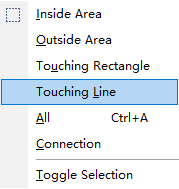

Altium Designer 当中,直接使用鼠标左键单击就可以选择一个原理图元件,也可以按下【Shift】键依次点击各个元件执行多选操作。更高级的多选方案是按下【S】按键,在弹出的选择命令菜单上选择相应的方式:

Inside Area:选中框选区域内的元件;Outside Ares:反向选中框选区域之外的元件;Touching Rectangle:鼠标拖出矩形进行框选;Touching Line:鼠标十字线单击进行选中;Connection:选中网络标号相同的元件;All:选择当前原理图上的全部元件。

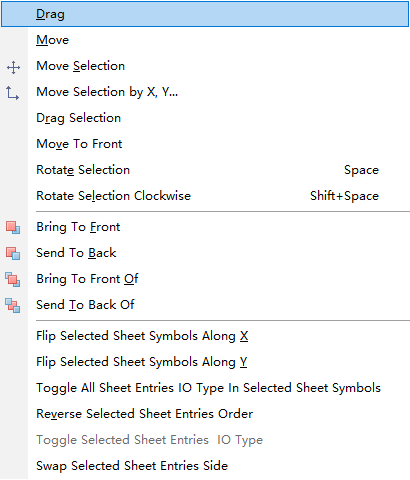

如果需要移动元件,则可以将鼠标指针放置到原理图元件上,按下鼠标左键直接进行拖动,此外也可以按下【M】键,在弹出的菜单中选择更为高级的操作,例如:选择Move Selection移动当前选中的所有元件,点选Move Selection by X,Y…则可以在

X 轴和 Y 轴上对元件进行精确的移动。

此时,如果还希望对元件进行旋转操作,除了选中元件并按下【空格】或者【Shift + 空格】键进行逆时针或顺时针旋转以外,还可以在按下【M】键以后选择

Rotate Selection、Rotate Selection Clockwise完成相同的操作。

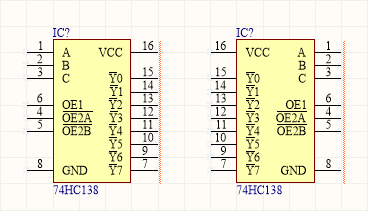

如果需要对元件进行水平或者垂直的翻转,则可以在当元件处于拖动状态时,按下【X】键或者【Y】键分别完成 X 轴或者 Y 轴的镜像,下面原理图就对其中一个 74HC138 译码器进行了翻转操作:

复制元件

选中需要操作的元件,执行菜单命令 Edit-Copy

或者按下快捷键 Ctrl + C

就能完成复制操作。但是,如果在按住【Shift】键的情况下拖动元件,则依然会复制元件,所不同的是所复制元件的网络标号会自增1。

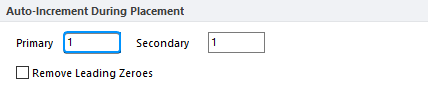

如果需要调整递增的幅度,则可以在原理图编辑界面按下快捷键 T +

P 或者点击菜单 DXP -> Preferences -> Schematic

->

General,找到Auto-Increment During Placement下的Primary参数,将其设置为所需的幅度值即可。

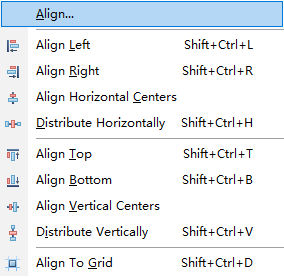

对齐元件

选择菜单 Edit -> Align

或者按下按键【A】可以进入排列与对齐命令菜单,其中Distribute Horizontally表示水平等间距对齐,Distribute Vertically则表示垂直等间距对齐:

连接操作

元件放置完成以后,就可以开始进行电气连接,从而让毫无关联的元件之间形成连接联系,进而构成完整的电路网络。

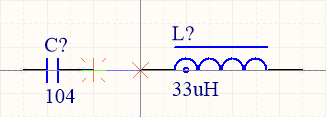

导线绘制

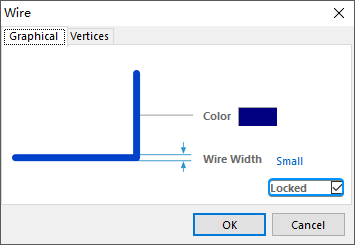

点击菜单栏上的 Place -> Wire 或者工具栏上的【Place Wire】图标,进行导线的放置,此时鼠标将会变为十字状态。选择一个元件管脚作为开始点,另一个元件管脚作为结束点,完成放置之后单击鼠标右键或者按下【Esc】键,结束本次导线绘制操作:

当处于导线放置状态时按下【Tab】键,或者双击原理图上已经绘制好的导线,可以对导线的属性进行相应的设置。例如设置为Locked状态,使导线不会由于误操作而发生移动:

在布线状态下,可以按住快捷键 Shift + 空格键 切换布线为 90° 直角、45° 度、任意角度:

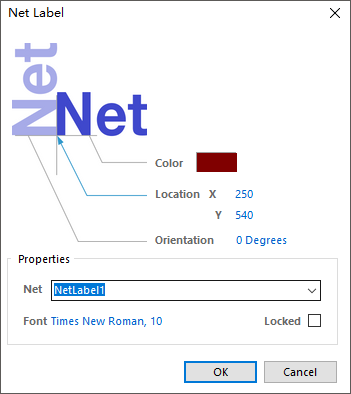

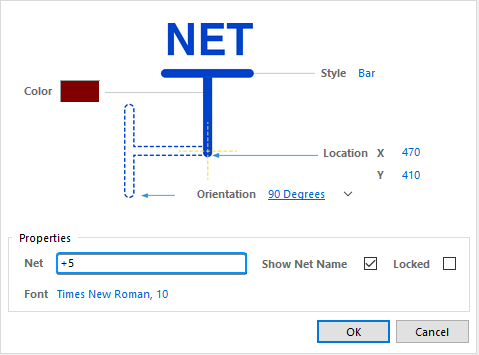

网络标号(Net Label)用于间接体现元件的连接关系,通过点击菜单栏命令 Place -> Net Label 或者按下【Place Net Label】按钮进行放置。同样的,处于放置状态时按下【Tab】键或者双击网络标号,可以对其属性进行设置:

Altium Designer

专门提供了电源和地的原理图符号,分别单击工具栏上的VCC Power Port

和 GND Power Port按钮即可以直接放置相应符号,

单击 Altium Designer 右上角的【Power Sources】图标,可以打开下图所示的常用电源端口菜单,这里可以选择所需的端口类型进行放置:

同样的,在放置过程中按下【Tab】或者放置以后双击该元件,可以对电源的属性进行设置:

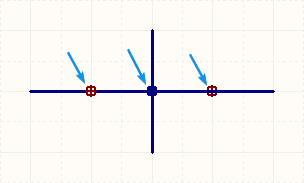

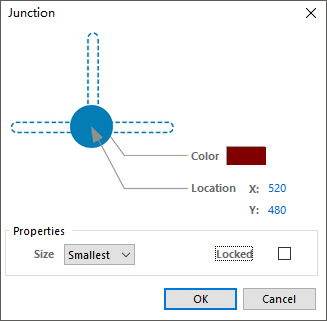

导线放置时,如果两条导线发生了交叉连接,则 Altium Designer 会自动放置交叉点(Junction);如果需要手动放置电气交叉点,则需要点击菜单上的 Place -> Manual Junction 命令或者使用快捷键【P + J】进行放置:

放置过程中按下【Tab】或者放置后双击交叉点,依然可以方便的进行属性设置:

页连接符

单张图纸当中,可以简单的通过网络标号(Net Label)实现电路的连接;但是,如果一个工程中存在多张原理图,此时就需要采用对应的连接符来完成原理图之间的连接。在这里,简单的总结和比较一下涉及网络连接的标识符。

| 符号 | 描述 |

|---|---|

|

电源端口,可以忽视掉工程的结构,因为其全局连接着所有原理图上出现的电源端口。 |

|

网络标号,单张原理图内部,可用来代替导线表达元件之间的连接关系;多张原理图当中,依然只能用于表达单张图纸内部连接关系。 |

|

端口,即可以用来表示单张原理图内部的连接关系,也可以用于体现多张原理图之间的连接,常用于 层次化的原理图设计。 |

|

跨页连接符,用于不同原理图之间的跨页连接,并且可以将其连接属性扩大至整个工程,常用于 扁平化的原理图设计。 |

|

图纸入口,总是垂直连接到下层的原理图端口,常见于 层次化的原理图设计。 |

|

图纸符号,即所需要链接的原理图的图纸符号,常见于 层次化的原理图设计。 |

添加网络标号

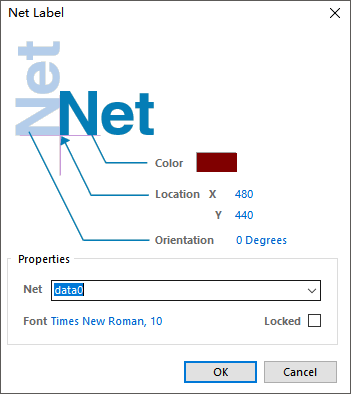

紧接上面的操作步骤,接下来为上面原理图当中的总线与信号线添加网络标号。单击绘图工具栏上的【Place Net Label】或者 P + N 快捷键,将网络标号放置到总线,放置过程中按下【Space】空格键可以旋转网络标号的方向,按下【F2】按键可以修改转网络标号的名称。

注意:必须将网络标号紧密的放在信号线或者总线上,使其成为信号线与总线相关的标识。

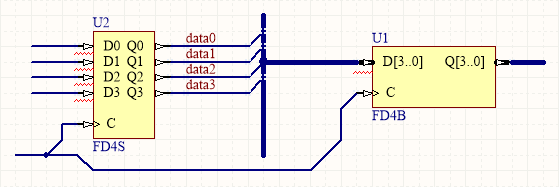

双击原理图当中的网络标号,可以打开 Net Label 网络标号对话框,这里可以对网络标号的名称、颜色、字体、位置进行设置:

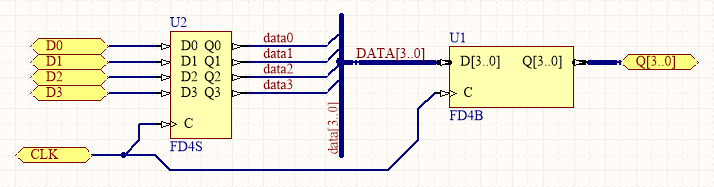

接下来为两条总线添加相应的网络标号,最终得到的效果如下图所示:

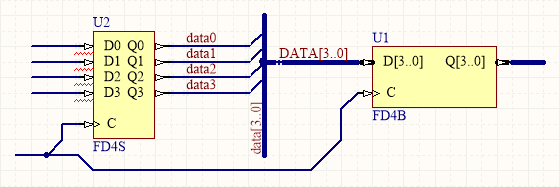

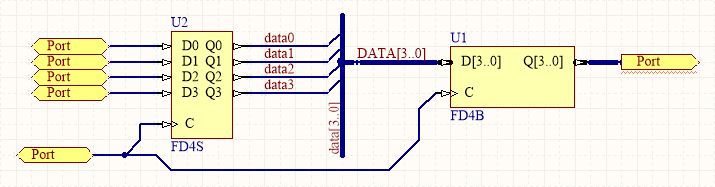

添加端口

接着上面的步骤,单击绘图工具栏上的【Place Port】或者 P + R 快捷键,为输入与输出信号线添加端口。按下【Esc】或者鼠标右键可以退出添加过程,并且同样可以通过【Space】空格键调整端口的放置方向,不过基于连线与端口符号接触的位置,Altium Designer 能够自动检测端口的方向:

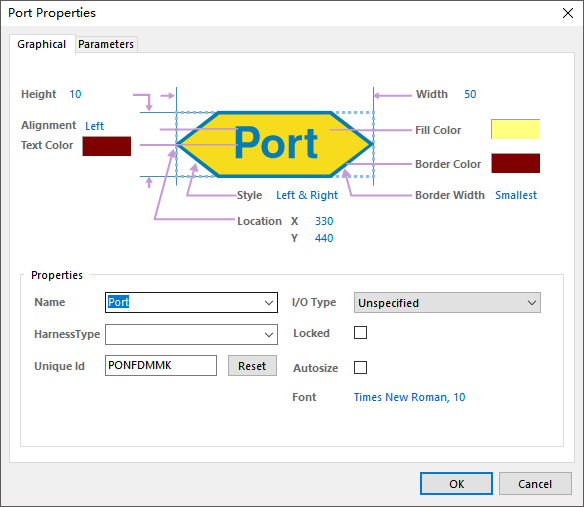

单击上面原理图上添加的端口标号,打开 Port Properties 端口属性对话框,这里可以对端口的名称、类型、唯一 ID、颜色等属性进行配置:

接下来修改端口名称,最终获得的原理图效果如下图所示:

添加信号束

信号线 Wire

用来表示各个元件端口之间的电气连接,总线 Bus

则用于表示一组相关的信号线,信号束 Harness

则是对多个信号进行逻辑分组,包含有信号束(Signal Harness)、

束入口(Harness Entry)、束连接器(Harness Connector)、束定义文件(Harness Definition File)这

4

个关键要素,将鼠标放置在信号束上,就可以获得其所包含的所有网络、总线、子信号束的详细信息。本小节需要打开一个全新的

PCB_Project1.PrjPCB 示例工程,然后双击打开 Sheet1.SchDoc

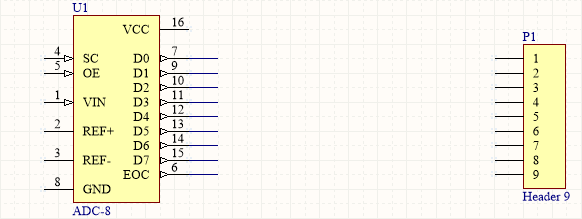

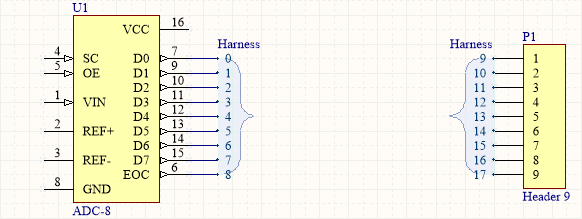

原理图文件:

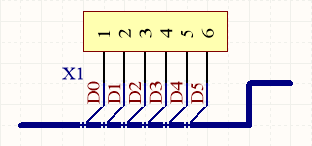

单击工具栏上的【Place Harness Connector】放置信号束连接器,按下【Space】空格键可以改变信号束连接器的方向,然后使用鼠标按需对其进行拉伸:

单击工具栏上的【Place Harness

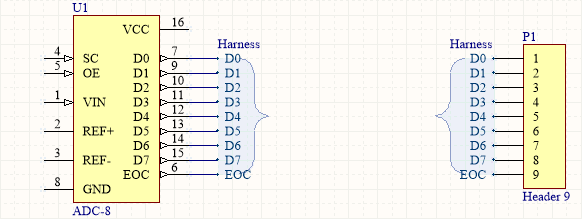

Entry】放置信号束入口到元件U1和P1的所有引脚:

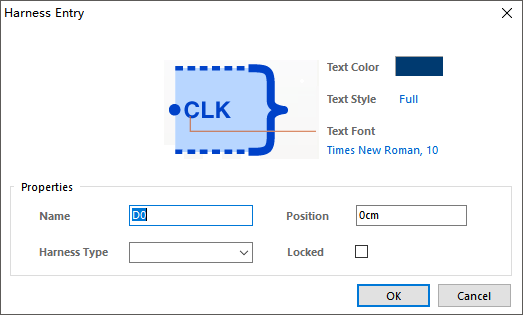

鼠标双击信号束编号0,打开 Harness Entry

信号束入口对话框,修改该信号束入口的名称:

当然,也可以选中信号束入口之后,直接按下【F2】按键更加方便的进行修改:

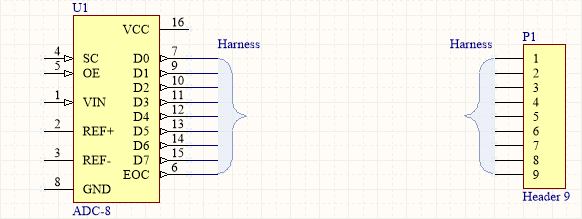

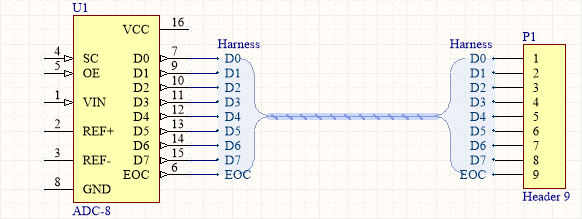

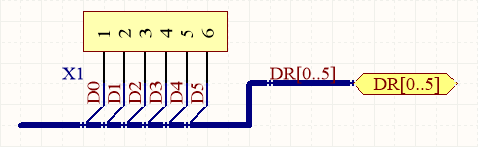

点击工具栏上的【Place Signal Harness】,使用信号束连接两个信号束连接器,最后保存原理图并关闭工程。

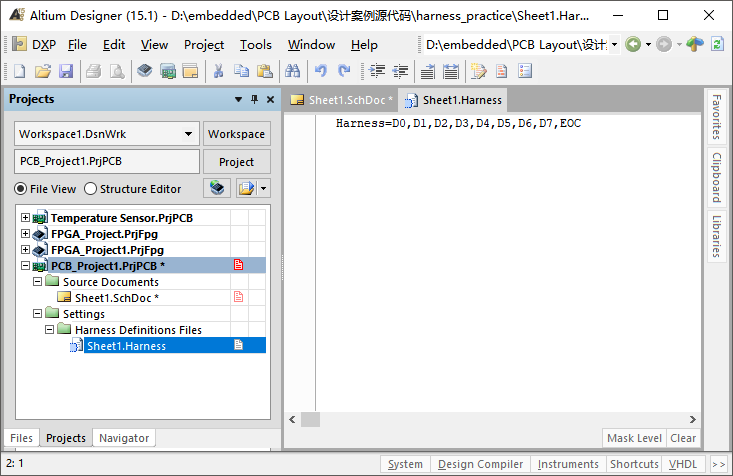

每个包含信号束的原理图都拥有一份信号束定义文件,该文件内定义了每个信号束的构成属性,打开主界面左侧的工程面板,依次展开 PCB_Project1.PrjPCB -> Settings -> Harness Definitions Files,即可以查看到信号束定义文件的内容。

总线放置

总线是一组具有相同电气特性的导线,即将具有相同电气特性的导线抽象为总线,以便于原理图的分析;总线上通过总线分支引出相应的各条导线,并以网络标号加以标识和区分;因此,总线、总线分支、网络标号密不可分。

首先,单击工具栏上的【Place Bus】图标,或者通过菜单栏上的 Place -> Bus 以及快捷键【P + B】放置总线;然后,通过工具栏上的【Place Bus Entry】图标,或者通过菜单栏上的 Place -> Bus Entry 以及快捷键【P + U】放置总线分支,下面是一个完成操作以后的示例:

原理图当中,两条总线上分别放置 1 个相同名称的 Port 端口,表示这两条总线是相互连接在一起的,接下来在上面例子基础上添加 1 个端口:

差分标识放置

高速电路设计当中,经常会使用到差分走线,例如: USB

接口的D+与D-差分信号、HDMI

接口的数据与时钟差分等等。 Altium Designer 当中,可以通点击菜单栏上的

Place -> Directives -> Differential Pair

分别将差分标识放置在一对信号线上。

注意:原理图设计时,习惯性在差分对信号线名称的后缀上添加

+和-或者_P和_N,

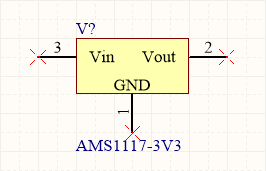

No ERC 放置

No ERC 是指忽略 ERC

检测,凡是指定了No ERC的元件管脚,在进行 ERC

检测时,出现的错误或者警告信息将会被自动忽略,并不会影响网络报表的生成。No

ERC 本身并不具备任何电气特性,主要用于原理图规则的检查。

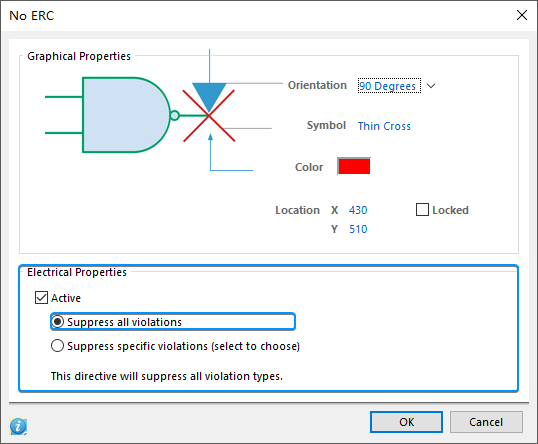

点击菜单栏上的【Place Non-Specific No ERC】,然后移动鼠标到需要忽略 ERC 检测的元件管脚,并且点击进行放置,完成后单击鼠标右键或者按下【Esc】键退出放置状态。

放置状态按下【Tab】键,或者放置完成之后双击 No ERC 检测点,即可设置其属性:

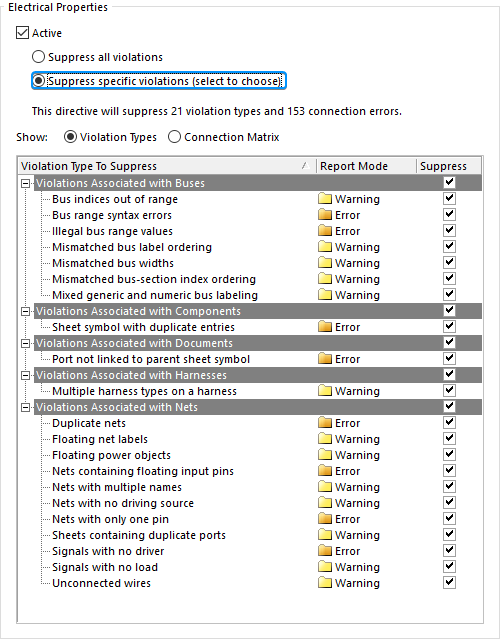

其中,Suppress all violations表示抑制所有违规信息,Suppress specific violations表示抑制指定的违规信息,选择后者时将会自动弹出复选框,并进一步指定需要抑制哪些违规信息:

辅助信息

原理图上出现的辅助信息没有电气属性,仅用于增强电路的可读性,或者添加相关的作者和版权版本。

![]()

| 符号 | 作用 | 符号 | 作用 |

|---|---|---|---|

|

放置线条(Place Line) |

|

放置矩形(Place Rectangle) |

|

放置多边形(Place Polygons) |

|

放置圆角矩形(Place Round Rectangle) |

|

放置椭圆弧(Place Elliptical Arcs) |

|

放置椭圆(Place Ellipses) |

|

放置贝塞尔曲线(Place Bezier) |

|

放置饼图(Place Pie Charts) |

|

放置文本字符串(Place Text String) |

|

放置图片(Place Graphic Image) |

|

放置超级链接(Place Hyperlink) |

|

智能粘贴(Smart Paste) |

|

放置文本框(Place Text Frame) |

需要特别说明的是,原理图设计时,可以通过放置线条来标识信号的方向或者对功能模块进行分块标识。执行 Altium Designer 右上角菜单上的【Place Line】图标,或者使用快捷键 ** P + D + L **,绘制一条普通的线条。

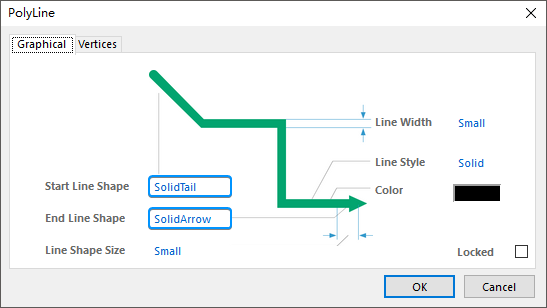

在放置状态按下【Tab】键,或者放置完成之后双击线条设置其属性:

此时,该线条就会变成一个可以用于标识电流方向的箭头:

【Place Line】也可以用于对电路功能进行分块,从而能够更加清晰的阅读电路原理图:

注意:【Place Wire】和【Place Line】是完全不同的两个概念,【Place Wire】具有电气性能,而【Place Line】没有电气性能,实际设计当中如果混淆使用,会造成电路的电气连接开路。

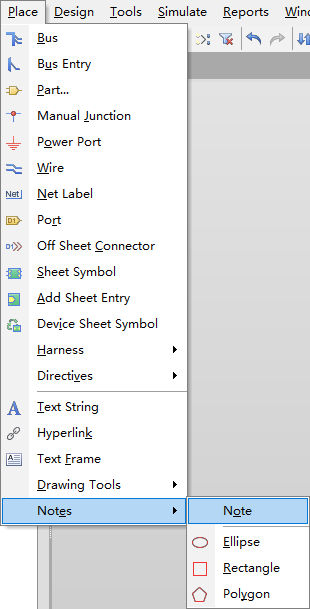

放置注释

Altium Designer 可以方便的在电路原理图当中放置注释框,注释框当中的内容可以通过鼠标点击进行最大或最小化。执行菜单命令 Place -> Notes -> Note 或者按下快捷键【P + E + O】为原理图添加注释:

完成放置以后,可以在注释框的属性设置里添加具体的注释内容,也可以点击左上角的红色三角标将该注释最小化:

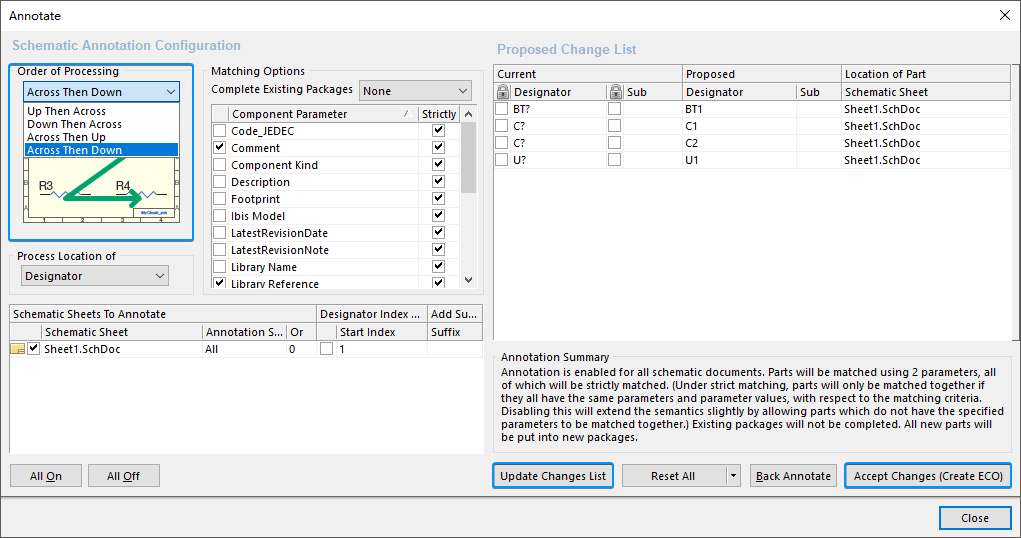

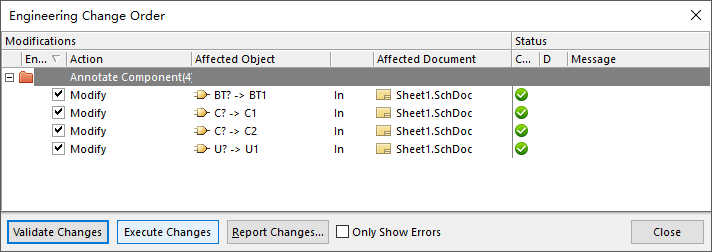

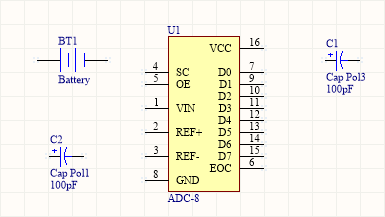

全局编号

Altium Designer 支持批量对元件的标志符(Designator)进行编号,执行菜单栏命令 Tools -> Annotation -> Annotate Schematics...或按下快捷键【T + A + A】进入 Annotate 注释对话框:

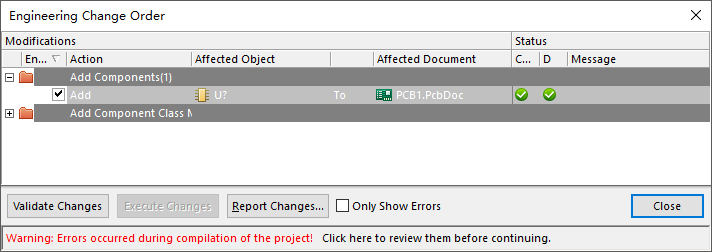

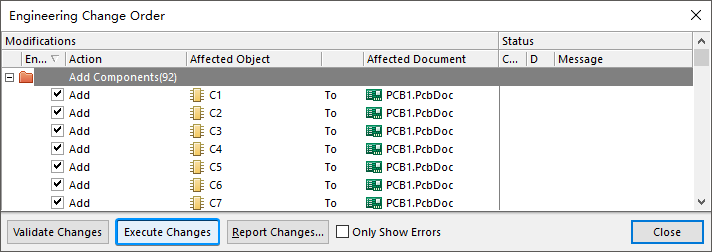

首先,在【Order of Processing】区域选择自动编号的方向,然后点击【Update Changes List】更新元件的标志符编号,然后点击【Accept Changes (Create CEO)】将更新后的编号写入原理图,此时会弹出 Engineering Change Order 对话框:

这里可以点击【Validate Changes】按钮验证变更,如果右侧 Check

栏出现全绿色的√就表示验证成功,接下来点击【Execute

Changes】按钮执行变更,从而完成原理图元件标志符的重新编号:

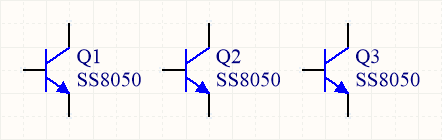

下面的表格整理了常用的元件标志符前缀:

| Designator | Designator | Designator | Designator |

|---|---|---|---|

R (电阻) |

RN (排阻) |

C (电容) |

EC (电解电容) |

FB (磁珠 |

U (芯片) |

MOD/U (模块) |

X (晶振) |

Q/T (三极管) |

D (二极管) |

ZD (整流二极管) |

LED (发光二极管) |

CON (连接器) |

J (跳线) |

K/SW (开关) |

BAT (电池) |

MH (固定通孔) |

H (标记点) |

TP (测试点) |

批量修改属性

Altium Designer

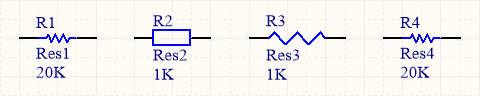

可以方便的对元件属性进行批量编辑,例如下面原理图当中,查找出20KΩ阻值的电阻并将其修改为10KΩ阻值(其它属性的修改操作也可以触类旁通):

选中电阻元件R1,在鼠标右键弹出的菜单上选择【Find Similar

Objects...】:

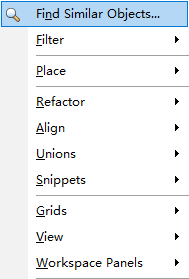

此时弹出的 Find Similar Ojbects

界面上,找到value = 20K那一栏并选择为【Same】,表示当前所要查找的是阻值为

20 千欧的电阻,同时勾选底部的【Select Matching】和【Run

Inspector】,然后点击【OK】按钮:

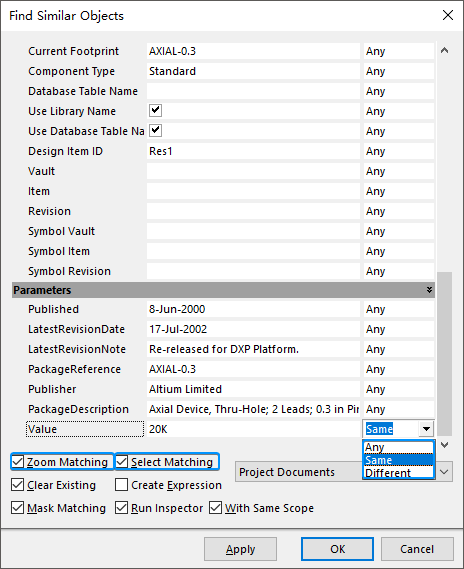

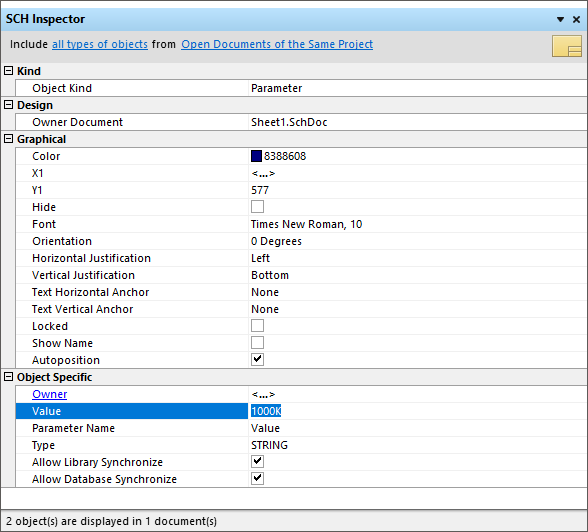

此时,Altium Designer 会放大并且自动选择 20

千欧电阻R1和R4,并且同时弹出 SCH

Inspector

对话框,在这里将value的值修改为1000K,然后关闭界面:

最终,原理图上的R1和R4被一次性的批量修改为1000K欧姆:

查询与跳转

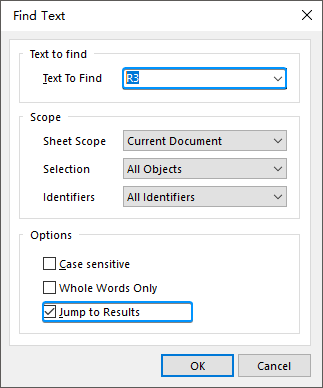

较大尺寸的原理图里不便于定位元件,此种情况下可以通过查询并且跳转来进行定位操作。按下快捷键【Ctrl

+

F】弹出文本查询对话框,在Text To Find输入框填写待查询的元件标志符、网络标号、管脚编号等文本信息,并且勾选Jump to Results选项,此时按下【OK】按钮即可跳转至指定元件。

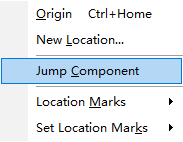

打开菜单栏命令 Edit -> Jump 或者按下快捷键【J】,弹出如下跳转操作相关的菜单:

Origin:跳转至原理图左下角的起始点;New Location...:跳转至指定的X和Y坐标值位置;Jump Component:跳转至指定标识符名称Designator元件;Location Marks:跳转至标记的位置;Set Location Marks:设置标记位置;

多页原理图

伴随着电路原理图复杂程度的日益提高,电路的设计已经不可能在一张绘图页上完成,其设计方法逐渐趋向于层次化(水平或者垂直)结构。即将电路图垂直或水平分割为多个模块,然后共同组成为一套完整的电路原理图。

- 如果采用扁平化(Flat)方式绘制,类似拼图的模式就是平坦式结构,一般通过跨页连接符(Off Sheet Connector)以及全局网络标号来完成逻辑上的连接。

- 如果采用层次化(Hierarchical)方式绘制,则每个模块可能由几个更为基础的模块构成,最后形成类似金字塔的层次化结构,此时采用原理图符号(Sheet Symbol)、原理图入口(Sheet Entry)、端口(Port)完成逻辑连接。

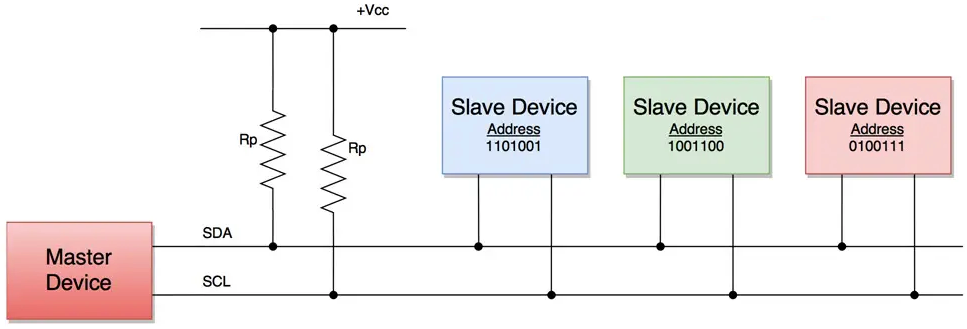

扁平化 Flat

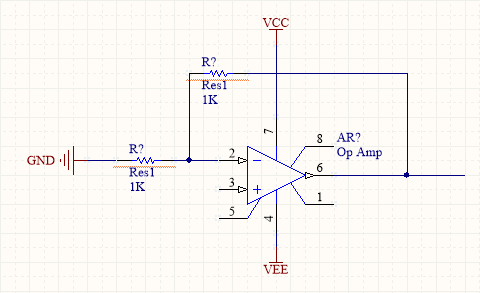

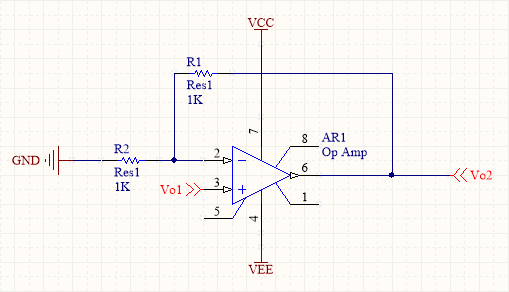

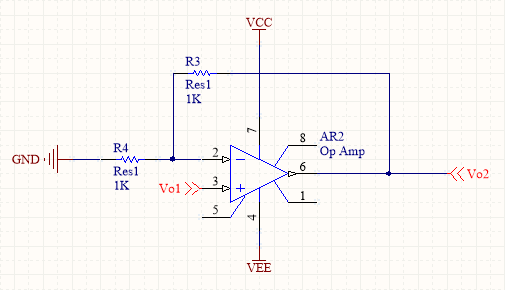

本小节将采用扁平化(Flat)方式绘制一个多页原理图,分别在 2 页原理图内绘制 2 个独立放大电路,然后在第 3 页绘制电路其它部分,最后通过网络标号Net Label与跨页连接符Off Sheet Connector实现每一页电路的连接。

首先,新建一个PCB_Project1.PrjPCB工程,并添加原理图文件Sheet1.SchDoc;然后,分别从Miscellaneous Devices.IntLib库中放置

2 个电阻元件Res1和 1

个运算放大器元件Op Amp,以及 1 个GND和 2

个电源VCC与VEE:

选择 Altium Designer 工具栏以及鼠标右键菜单上的 Place ->

Off Sheet Connector 或者按下P +

C快捷键,然后在放大器的输入/输出端分别放置 2

个跨页连接符Vo1和Vo2,最后自动分配网络标号:

然后,再新建一个原理图文件Sheet2.SchDoc,重新从Miscellaneous Devices.IntLib库中放置

2 个电阻元件Res1和 1

个运算放大器元件Op Amp,以及 1 个GND和 2

个电源VCC与VEE。

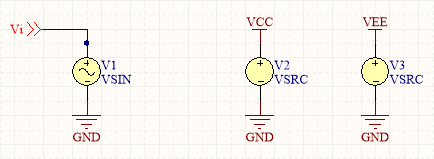

最后,新建一个原理图文件Sheet3.SchDoc,从Simulation Sources.IntLib库中放置

2 个VSRC和 1

个VSIN,以及相应的GND、VCC、VEE,并且放置跨页连接符Vi,以及分配唯一网络标号。

分别双击原理图上的VSRC元件,打开各自的属性对话框,将V2设置为+12V,将V3设置为-12V。

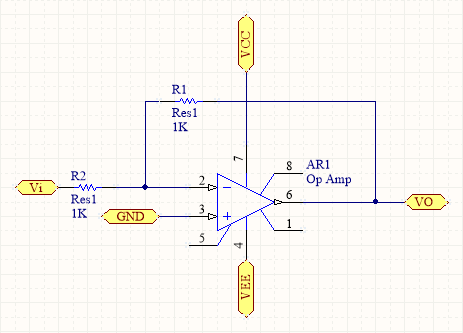

层次化 Hierarchical

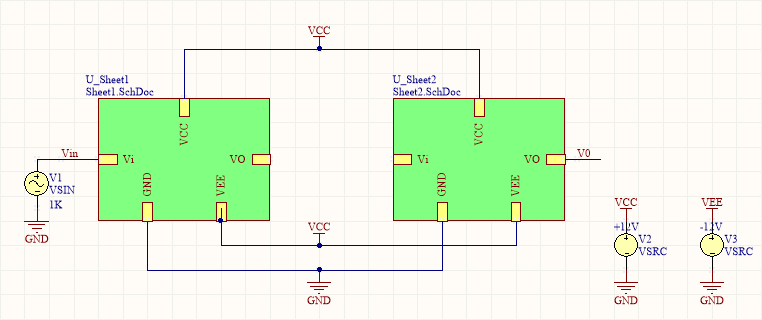

本小节改为采用层次化(Hierarchical)方式绘制多页原理图,分别在 2

页原理图内绘制 2 个独立放大电路,最后通过原理图入口 Sheet

Entry

关联这些原理图,最终组合为一个完整的多级放大电路。继续新建一个PCB_Project2.PrjPCB工程,然后添加Sheet1.SchDoc原理图文件,并且添加

Port

端口Vi、GND、VO、VCC、VEE,并自动化生成相应网络标号。

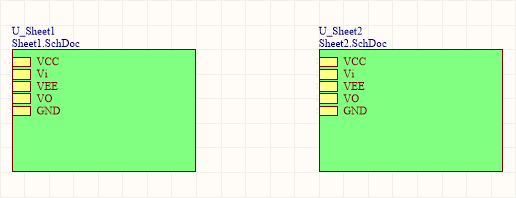

同样的,再新建一个相同内容的Sheet2.SchDoc原理图文件,并自动化生成网络标号:

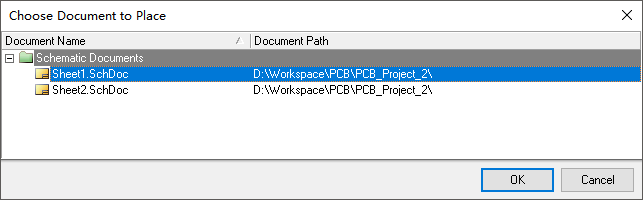

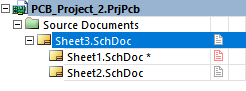

新建Sheet3.SchDoc原理图文件并且选中,然后依次选择主界面菜单上的

Design → Create Sheet Symbol From Sheet or HDL

或者快捷键 D + Y,此时会弹出 Choose Document to

Place

对话框,双击或者选择Sheet1.SchDoc以后点击【OK】:

接下来以同样的步骤选择并且放置Sheet2.SchDoc的原理图符号:

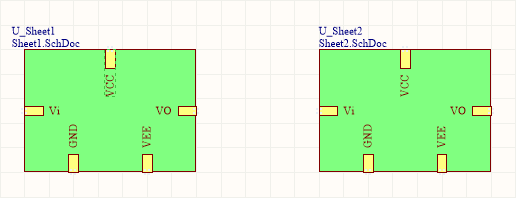

选择主界面菜单上的 Project -> Compile PCB Project 编译当前工程,此时可以看到左侧工程面板的原理图文件层次结构发生了变化:

拖动上图中的原理图入口标识 Sheet Entry,重新进行排版布局,便于后续进一步处理:

最后,从Simulation Sources.IntLib库中放置VSRC和VSIN元件,以及相应的GND、VCC、VEE,然后自动分配网络标号,同时勾选V1的参数,并且设置V2和V3的元件属性值为+12V和-12V,最终呈现的原理图效果如下:

检查与编译

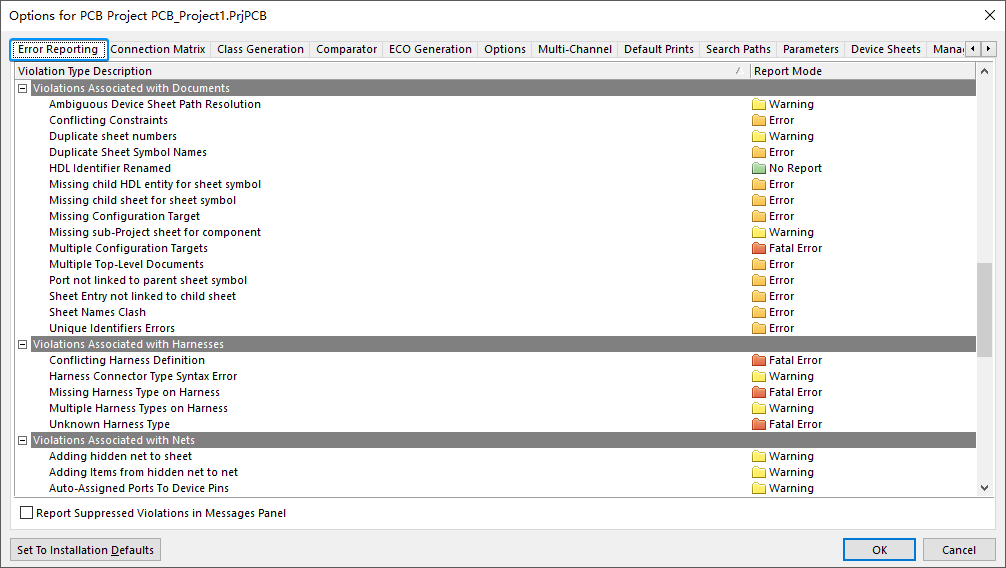

原理图设计完成之后,可以利用 Altium Designer 自带的 ERC (Design Rule Check) 校验功能进行检查,避免一些常规性错误的同时,确保后续能够正确的导出网表并生成 PCB。首先,将鼠标移动至左侧的工程面板,然后右键选择 Project Options;或者打开顶部菜单栏的 Project -> Project Options;单击【Error Reporting】选项卡进入错误检查设置界面,选择需要进行校验的规则以及对应的处理措施:

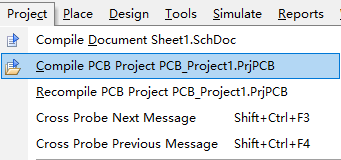

完成 ERC 设计规则检查的相关设置之后,可以通过执行菜单栏命令 Project -> Compile PCB Project.PrjPcb 执行电路原理图的编译工作:

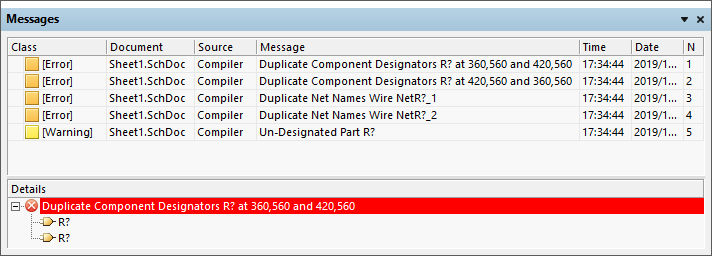

如果工程中的原理图在编译时发生错误,则会自动弹出 Messages 对话框并列出相关的错误信息,双击具体错误即可自动跳转至原理图对应位置:

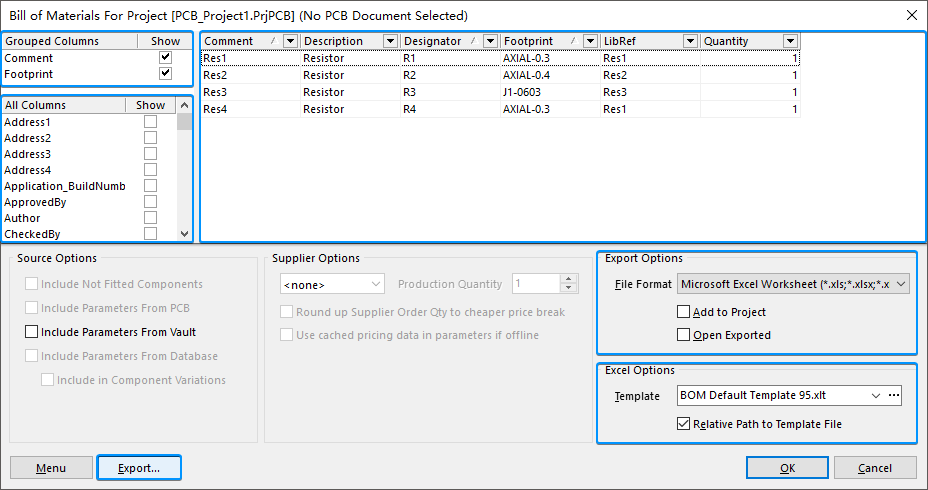

物料清单 BOM

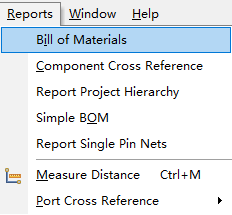

BOM(物料清单,Bill of Material)是在原理图设计完成之后,将电路中涉及的电子元件信息导出,便于后期采购和生成 PCB。执行菜单命令 Reports -> Bill of Materials 或者按下【R + I】快捷键:

此时就会自动进入 BOM 导出设置界面,单击该界面左下角的【Export...】按钮,将所生成的 BOM 表保存至硬盘的指定位置,一般情况下就保存在当前工程目录的下面:

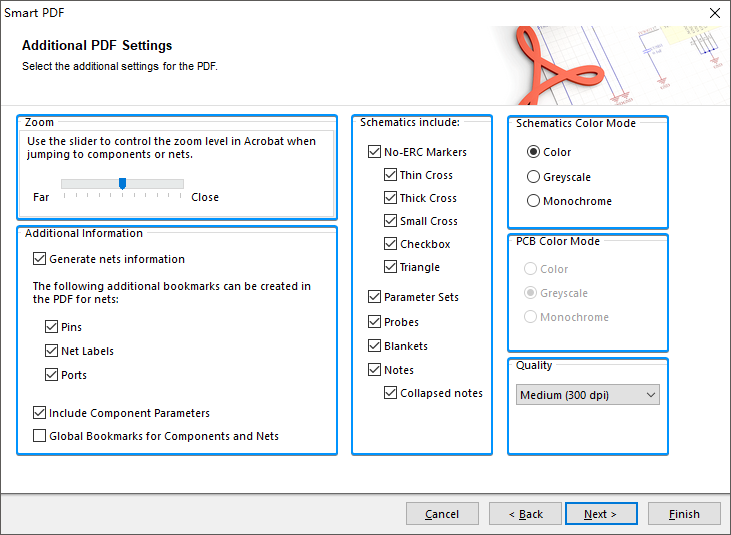

输出打印

原理图设计完成之后,可以将其以 PDF 格式导出,以便于提供给其它开发人员阅读,执行菜单命令 File -> Smart PDF 进入 PDF 创建向导,并且单击【Next】按钮:

快捷键总结

鼠标

| 操作 | 用途 | 操作 | 用途 |

|---|---|---|---|

| 长按鼠标【左】键 | 拖动元件 | 长按鼠标【右】键 | 拖动原理图 |

| 双击鼠标【左】键 | 设置元件属性 | 按住鼠标【滚轮】并且移动 | 放大/缩小原理图 |

| 【Alt】 + 鼠标单击 | 高亮指定元件 | 【Shift】 + 鼠标拖动 | 标识符递增复制 |

视图

| 操作 | 用途 | 操作 | 用途 |

|---|---|---|---|

| 【V + D】 | Fit Document,原理图全屏显示 | 【V + F】 | Fit All Objects,放大元件区域 |

| 【Page Up】 | Zoom In,以鼠标为中心进行放大 | 【Page Down】 | Zoom Out,以鼠标为中心进行缩小 |

| 【V + E】 | Selected Objects,放大当前选中的元件 |

排列

| 操作 | 用途 | 操作 | 用途 |

|---|---|---|---|

| 【A + L】 | Align Left,向左对齐 | 【A + R】 | Align Right,向右对齐 |

| 【A + T】 | Align Top,向上对齐 | 【A + B】 | Align Bottom,向下对齐 |

| 【A + D】 | Distribute Horizontally,水平等间距对齐 | 【A + I】 | Distribute Vertically,垂直等间距对齐 |

其它

| 操作 | 用途 | 操作 | 用途 |

|---|---|---|---|

| 【J + C】 | 跳转至元件 | 【Ctrl + F】 | 查找元件上的文本 |

| 【P + W】 | Place Wire,放置导线 | 【P + B】 | Place Bus,放置总线 |

| 【P + P】 | Place Part,放置元件 | 【P + N】 | Place Net Label,放置网络标号 |

| 【P + T】 | Place Text String,放置字符标注 | 【E + D】 | Delete,删除选中元件 |

| 【T + P】 | Preferences,系统参数设置 |

PCB 基本结构

PCB 是(印制电路板,Printed Circuit Board)的英文缩写,主要以绝缘覆铜板为基材,经过印刷、蚀刻、钻孔等处理工序,将电路元件的连接关系用一系列导电图形、孔位制作出来,最后剪裁为特定的外形尺寸。根据覆铜层数的不同,可以将 PCB 分为如下 3 种:

- 单面板(Single Layer):仅有一面覆铜,通常情况下,元件集中放置在没有覆铜的一侧(即 Component Side),覆铜导线则集中放置在另一侧(即 Solder [ˈsəʊldə],焊料 Side);

- 双面板(Double Layer):两面都有覆铜,上下两个覆铜层分别称为顶层(Top Layer)和底层(Bottom Layer),两层之间采用过孔进行连接;通常情况下,顶层主要放置元件,底层主要用于焊接与走线;

- 多层板(Multi Layer):除了顶层和底层之外,中间还包含有信号层、中间层、电源层、接地层,每层之间相互绝缘,并且采用过孔进行连接;多层板由于采用了独立的电源层和接地层,从而有效的提升了电路可靠性。

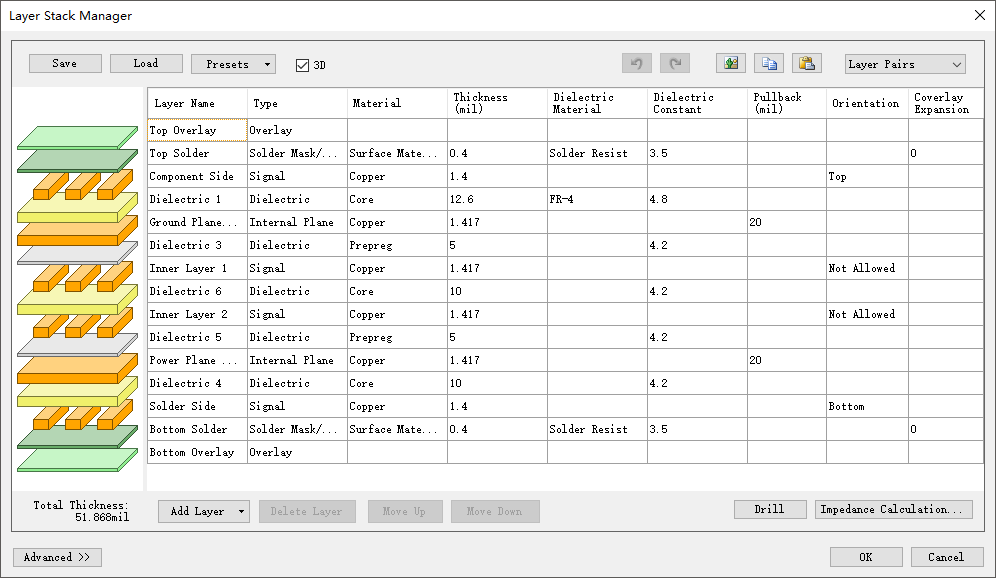

工作层

Altium Designer 提供的 PCB

编辑器包含有多个工作层,这些工作层可以更具体的划分为信号层(Signal

Layers)、内部电源/接地层(Internal

Planes)、机械层(Mechanical

Layers)、屏蔽层(Mask

Layers)、丝印层(Silkscreen

Layers)以及其它层(Other Layers),在 Altium

Designer 的 PCB 编辑界面下,选择工具栏的 Design -> Layer

Stack Manager... 或者按下快捷键【D +

K】可以打开板层管理器,然后选择Presets下拉菜单中的Six Layer打开

6 层 PCB 的剖面图:

信号层(Signal Layers):主要用来放置铜膜导线和元件,为电气信号提供传输通道,Altium Designer 可以设置多达 32 个信号层,包括 1 个

顶层(Top Layer)和 1 个底层(Bottom Layer),以及 30 个中间信号层(Signal Layer),每层都可以设置不同的颜色以便于区分。内部电源/接地层(Internal Planes [pleinz],平面):也称为内电层,主要用来铺设电源和接地,由大块的铜膜覆盖而成,可以提升电路板的工作稳定性,Altium Designer 最多可设置 16 个内电层。相同的内部电源/接地层可以分为几个区域(内电层分割),分别用来安置不同的电源和接地,例如将接电层分割为不同区域,分别用来放置电源地、模拟地、数字地。

机械层(Mechanical Layers):主要用来放置 PCB 生产与装配相关的各种标注,例如 PCB 的外形尺寸、焊盘与过孔类型等等,Altium Designer 最多可以设置 16 个机械层。

屏蔽层(Mask Layers):是阻焊层(Solder Mask)和助焊层(Paste Mask)的总称;阻焊层除留出焊点位置以外,其余部分采用阻焊膜将铜膜导线覆盖,排开焊锡避免波峰焊时发生桥接,主要包括顶层阻焊层(Top Solder)和底层阻焊层(Bottom Solder)。助焊层则是在需要焊接的位置,涂一层助焊剂以增强焊盘的着锡能力,主要包括顶层助焊层(Top Paste)和底层助焊层(Bottom Paste)。

丝印层(Silkscreen Layers):用于印制电子元件相关的信息,例如元件编号、外形轮廓、设计者、设计日期。涂料采用了不导电绝缘材料,主要分为顶层丝印(Top Overlay [ˌəʊvəˈleɪ],涂层)和底层丝印(Bottom Overlay)。

其它层(Other Layers):主要包括用于提供钻孔位置信息的钻孔引导层(Drill [drɪl],钻孔 Guide)和钻孔视图层(Drill Drawing),前者主要兼容旧式电路板工艺,现代工艺主要使用后者来提供钻孔参考信息;用于定义元件和导线放置区域(电气边界)的禁止布线层(Keep-Out Layer),自动布线时元件和导线必须放置在禁止布线层划定的区域。代表所有信号层的多层(Multi-Layer),该层放置的元件会自动放置到所有的信号层上。

注意: 实际工作环境下,并不会使用到 Altium Designer 提供的全部层,例如:双面板只有底层和顶层没有中间层,而顶层信号层和顶层丝印层等工作层在物理上相互重合,机械层只是为了便于 PCB 的加工与制作。

正/负片层

正片层即 PCB

上用于走线的信号层,可以用Track、Polygon进行大块的敷铜填充操作。负片层则正好相反,即默认整层是敷铜的,而铺线的位置则是未覆铜的分割线。

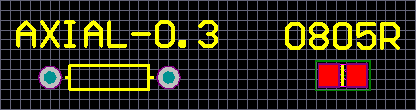

元件封装 Footprint

元件封装(Footprint)是指元件实际焊接至 PCB

电路板时,所形成的焊接位置与外形尺寸以及引脚间距。相同元件可以有不同封装方式,同种元件也可能共用一种封装。例如常用的电阻,可能拥有插针式(AXIAL-xx)和贴片式(SMD),其中贴片元件的封装规格用

4 位数字表示,前 2 位表示长度,后 2

位表示宽度,例如0603R、0402R、0201R、0805R。

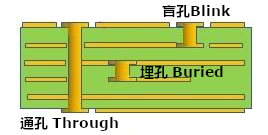

过孔 Via

过孔是镀铜的的金属小孔,用于 PCB

不同工作层之间的电气连接,可以分为通孔(Through,连接顶层与底层并贯穿整个

PCB 的)、盲孔(Blind,一端位于 PCB

表面,另一端位于 PCB

中间的工作层)、埋孔(Buried,用于 PCB

中间两个工作层之间的连接)。

注意:出于信号完整性的考虑,PCB 设计当中应该尽量减少过孔的使用;如果使用了过孔,则尽量避免采用盲孔和埋孔,它们不但增加了 PCB 的加工难度,也带来了大量电气安全性方面的问题,同时也为后期的电路调试埋下了隐患。

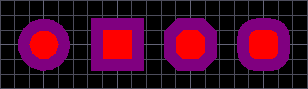

焊盘 Pad

焊盘用来将电子元件固定并连接在 PCB 电路上,每个焊盘都拥有独立编号,以便于和元件引脚对应,Altium Designer 提供了多种不同形状的焊盘:

铜膜导线 Track

铜膜导线 是覆铜板经过加工以后,在 PCB 上形成的实际走线,主要用于连接 PCB 上的各个焊盘,因其在电路中载流能力的不同,设计电路时所选取的宽度也有所不同。不同工作层上的铜膜导线通过 过孔 进行连接。而 覆铜 是指在 PCB 布线完成以后,在未进行布线的区域铺设铜膜,一方面加大电路的接地面积提升抗干扰能力,另外也利于元件的散热。敷铜可以与电路网络相连接,也可以独立存在,不同区域的敷铜可以连接不同的网络,但是大多数情况下敷铜都用于接地。

此外为了降低 PCB 上的导线、过孔、焊盘及元器件之间的相互干扰,需要在其之间留出一定的间隔距离(即安全距离),该选项可以在 Altium Designer 的布线规则当中进行配置。

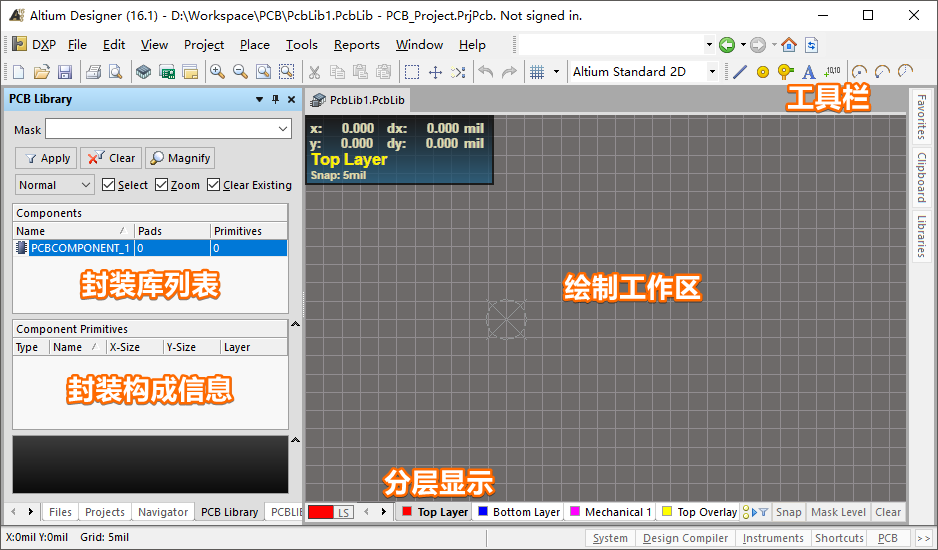

PCB 封装库

电路原理图设计完成之后,原理图上的元件将通过 PCB 封装库映射至真实的 PCB 印刷电路板上面。因此,不能随意调整 PCB 封装库中元件的尺寸,而应按照元件官方的规格说明书进行精确的绘制。

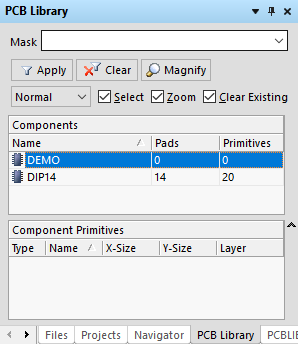

点击菜单 Project -> Add New to Project -> PCB

Library 向工程添加一个 PCB

封装库文件PcbLib1.PcbLib,然后将左侧的项目选项卡切换至【PCB

Library】即可进入如下 PCB 库的编辑界面:

通常情况下,一个元件的 PCB 封装会包含以下几个基本组成部分:

- 焊盘:PCB 上提供给电子元件引脚焊接的载体;

- 管脚序号:用于匹配原理图元件电气连接关系的序号。

- 丝印层:位于 PCB 最表层,用于放置元件标识或者文字性描述;

- 阻焊层:指 PCB 上被绿油覆盖的部分,主要用于保护下面的 PCB 走线,避免铜线氧化或者回流焊时粘锡;

- 1 脚/极性标识:定位元件方向的标识符号;

- 过孔:双面或多面 PCB 上用于连通各层的公用导通孔;

- 安装孔:用于固定 PCB 电路板的开孔;

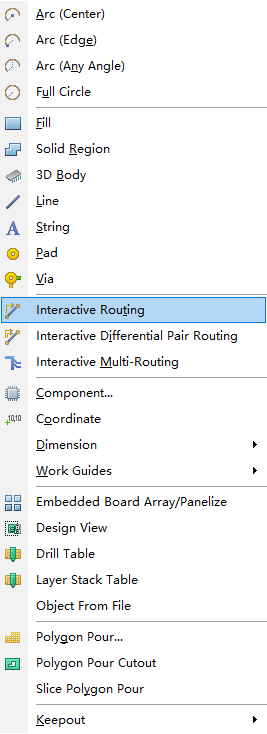

通过 Altium Designer 顶部工具栏可以方便的放置圆弧、多边形、线条、焊盘、过孔等元素,下面的表格罗列了工具栏上放置相关的按钮及功能:

| 符号 | 作用 | 符号 | 作用 |

|---|---|---|---|

|

放置线条(Place Line) |

|

按边缘放置圆弧(任意角度)(Place Arc by Edge(Any Angle)) |

|

放置焊盘(Place Pad) |

|

放置正圆形(Place Full Circle Arc) |

|

放置过孔(Place Via) |

|

放置填充(Place Fill) |

|

放置字符串(Place String) |

|

放置固态区域(Place Solid Region) |

|

放置坐标(Place Coordinate) |

|

阵列式粘贴(Paste Array) |

|

按中心放置圆弧(Place Arc by Center) |

|

放置 3D

元件体(Paste 3D Body) |

|

按边缘放置圆弧(Place Arc by Edge) |

|

多边形填充挖空(Polygon Pour Cutout) |

2D 封装

Altium Designer 创建封装的方法包含自动向导创建和手动绘制创建两种方式,自动向导创建适用于引脚数目比较多且形状较规范的封装,手动绘制创建适用于引脚数目较少或者形状不规范的封装。

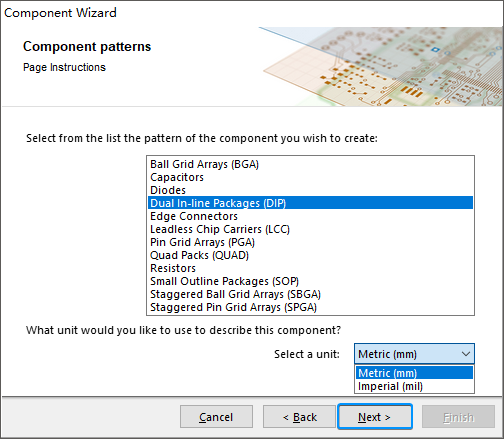

自动向导创建

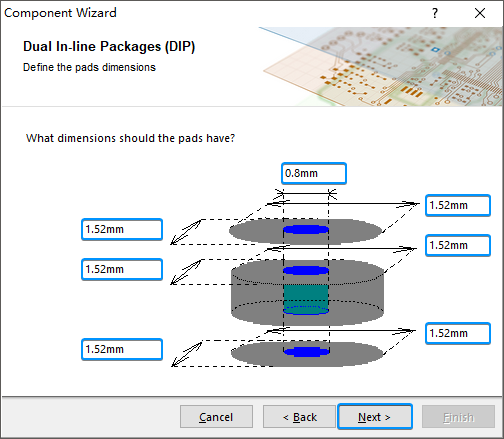

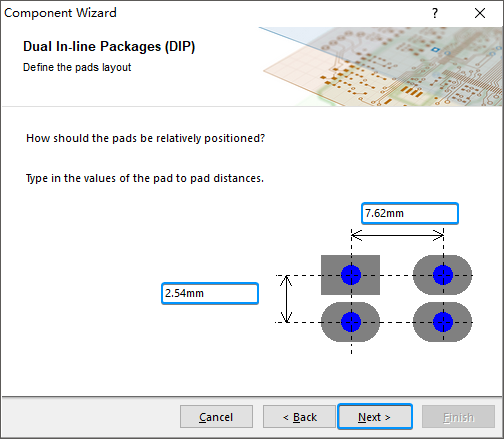

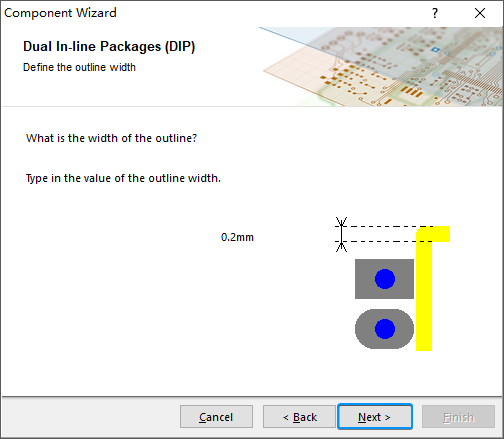

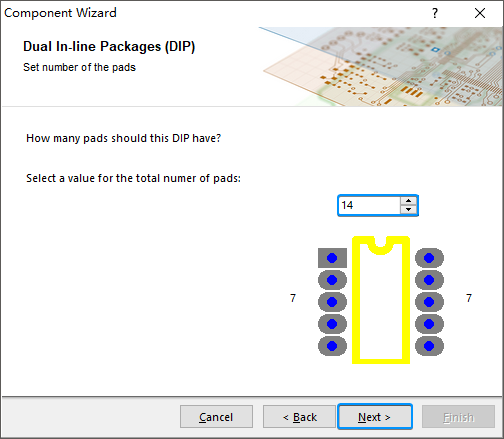

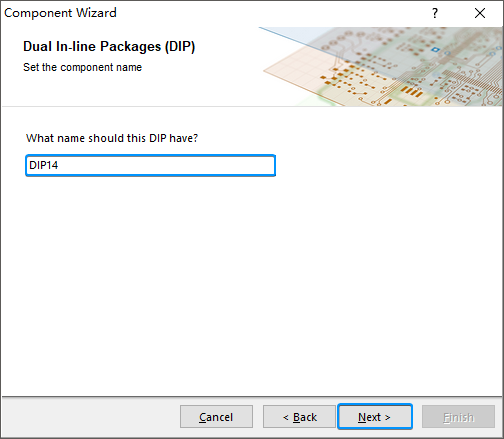

鼠标右键点击 Altium Designer 左侧工程面板的 Components 界面,选择【Component Wizard...】打开下图所示的封装创建向导:

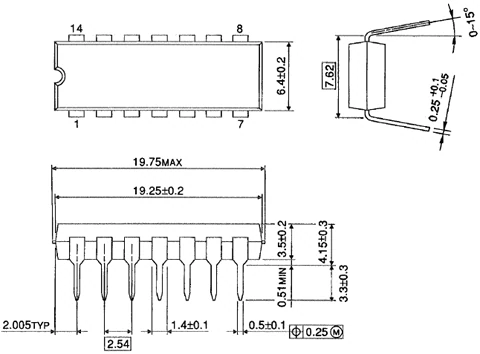

参考上面截图中提供的 DIP14 封装尺寸数据,在封装创建向导当中填写 焊盘尺寸(Pads dimensions )、焊盘间距(Pad layout)、元件轮廓宽度(Outline Width)、焊盘个数(Pads Number) 等参数,最后设置该 DIP 封装的名称:

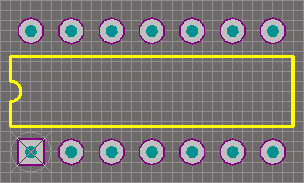

最终,Altium Designer 会根据创建向导中填写的数据信息,自动生成如下的 DIP14 封装:

手动绘制创建

本章节开始的内容中,已经通过执行 Altium Designer 菜单栏上的

File -> New -> Library -> PCB Library

新建一个名为PcbLib1.PcbLib的 PCB

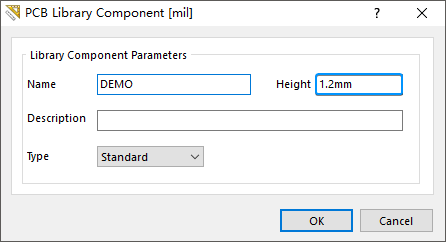

库文件,并随之自动生成了一个名为PCBCOMPONENT_1的封装,双击该封装将其重新命名为DEMO:

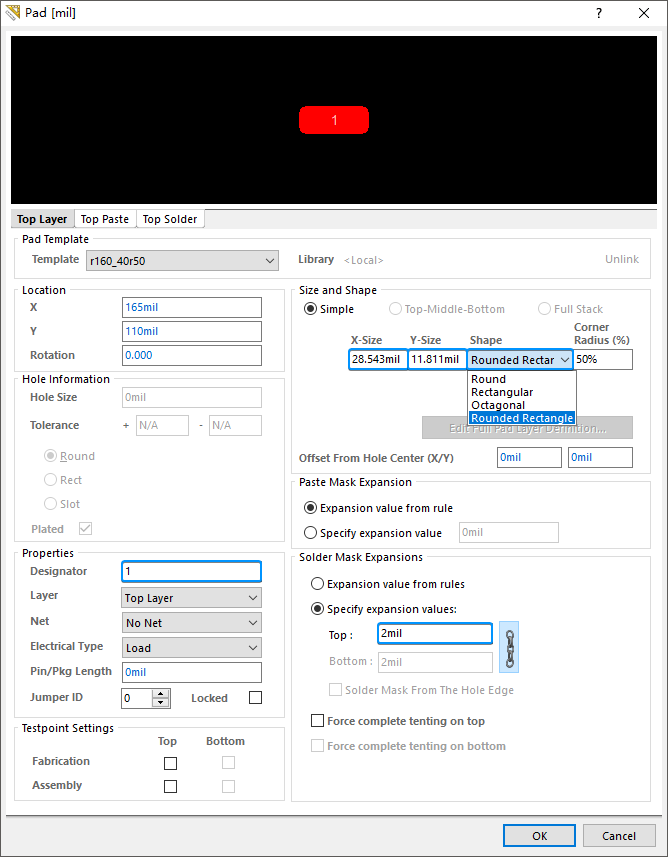

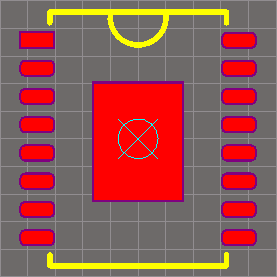

执行菜单栏命令 Place -> Pad

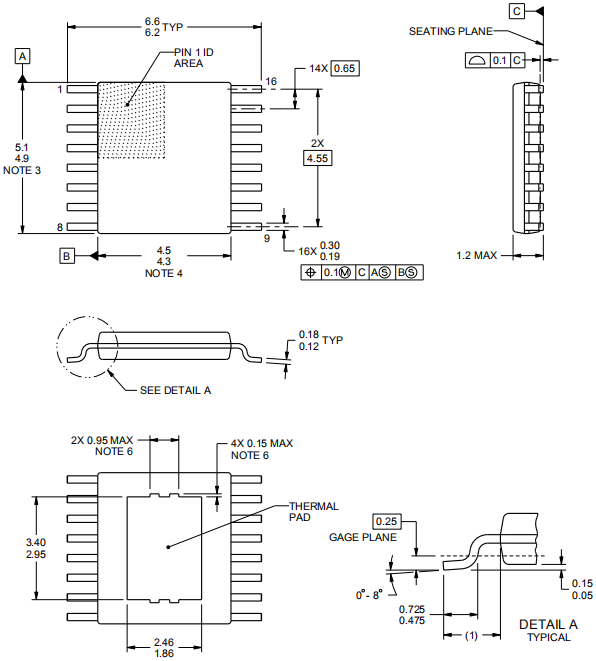

放置焊盘,在放置状态按下【Tab】键设置焊盘属性,选择形状为圆角矩形Rounded Rectangular的顶层焊盘Top Layer。为了抵消元件安装时产生误差,焊盘制作时通常会加入适当的补偿值,这里为了方便理解与简化计算,仅根据元件实际尺寸进行绘制,如下截图是德州仪器生产的

TPS54550 同步降压转换器的封装尺寸数据:

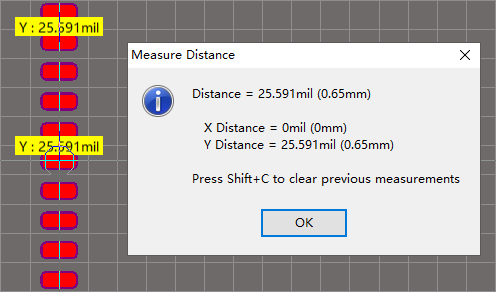

数据手册显示当前焊盘的最大长度与高度分别为0.725mm与0.3mm,焊盘中心之间的纵向间隔距离为0.65mm,左右两排焊盘横向的间隔距离为((6.6mm - 4.5mm)/2 - 0.725mm) * 2 + 4.5mm = 5.15mm,同时阻焊的宽度要设置为2mil:

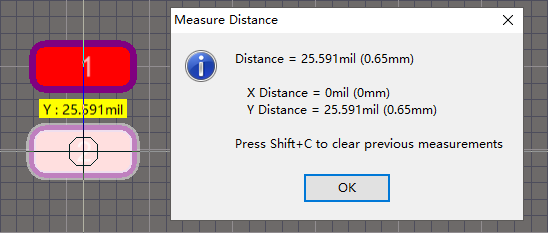

注意:选择菜单栏命令Reports -> Measure Distance或按下快捷键【Ctrl + M】可以调出测量工具,完成测量后按下【Shift + C】即可取消。

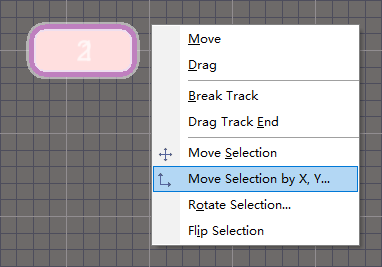

按照指定间隔距离摆放焊盘主要存在两种方式,第 1

种是在选中并且复制一个焊盘以后将两者重合在一起,然后鼠标点击 Altium

Designer 菜单栏上的 Edit -> Move -> Move Selection by X,

Y...

或者按下快捷键【M】在弹出的移动菜单上选择Move Selection by X, Y...,即采用X

Y 坐标轴移动方式完成横向或者纵向的移动:

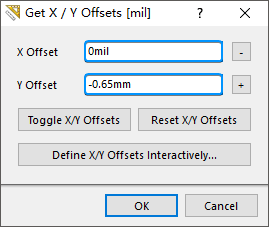

然后在 Y Offset 上填写-0.65mm,即向 Y

轴偏移0.65毫米,点击【OK】:

完成移动以后,调用测量工具对1和2两个焊盘的间隔距离进行测量,得到结果即为上面设置的0.65mm:

这种采用X、Y坐标轴移动的方式需要逐个元件进行操作,速度较慢而且容易出错,因此这种情况下通常会采用更为便捷的第

2

种方式:首先放置一个已经设定好尺寸的焊盘并且选中复制,然后鼠标点击菜单栏上的

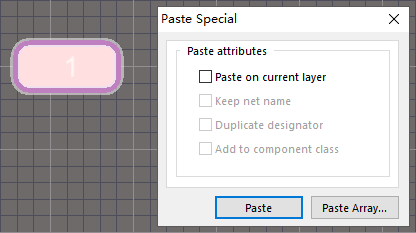

Edit -> Paste Special... 或者按下快捷键【E +

A】弹出特殊粘贴对话框,点击粘贴阵列按钮【Paste Array...】:

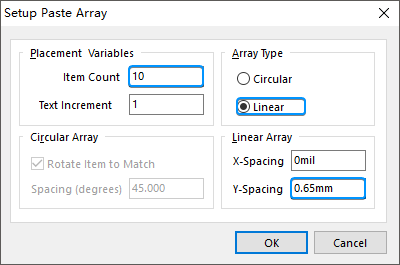

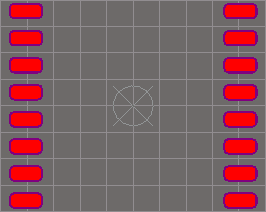

接下来进入到粘贴阵列配置界面,分别将粘贴数量Item Count设置为10,阵列类型Array Type选择为Linear,线性阵列Linear Array的

Y

轴间隔填写为0.65mm,最后鼠标点击【OK】:

此时将会自动返回至封装库绘制区域,鼠标点击需要生成阵列的焊盘,即可一次性自动生成

10 个间距为0.65mm的焊盘:

注意:采用阵列粘贴方式批量生成焊盘之后,最初的

1号焊盘将会被冗余出来,此时需要手动将其删除,避免后续 DRC 校验时引发错误。

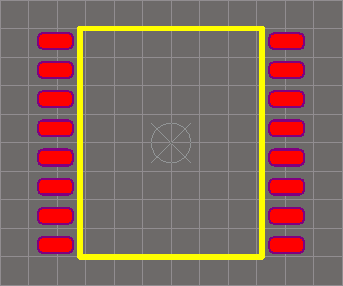

接着采用同样方式放置11 ~ 20号焊盘,并通过 X 和 Y

轴偏移方式使左右两组焊盘保持5.15mm间隔距离,然后鼠标选择菜单栏上的

Edit -> Set Reference -> Center 或按下快捷键【E +

F + C】将绘制区域的原点设置为中心点:

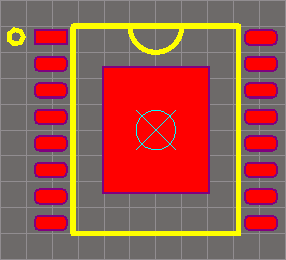

接下来向丝印层 Top Overlayer

绘制元件的丝印,丝印的线宽一般选择为5mil,由于1mil = 0.0254mm,那么换算为毫米单位应为1.27mm,而元件本体的长度和宽度分别为5.1mm和4.5mm,这里采用辅助线向

X 和 Y 轴偏移的方式来定位尺寸:

接着根据 TPS54550

的封装尺寸数据来放置长度3.40mm宽度2.46mm的散热焊盘,同时将

1 号引脚设计为矩形,并添加方向丝印:

注意:上面的示例当中,焊盘的长度与宽度均按照元件引脚的最大尺寸进行设计,最终呈现的效果会发现焊盘尺寸过小而间距过大,因此实际生产环境下必须增加相应的补偿值。

最后,为了方便其它工程师了解该元件的封装高度,需要再添加高度相关的信息,双击

PCB 封装列表 Components

上的元件DEMO,在弹出的对话框中输入高度值1.2mm:

如果遇到元件丝印覆盖了引脚焊盘的情况,此时可以鼠标选中菜单栏上的 Edit -> Slice Tracks 或者按下快捷键【E + K】剪断丝印,并将覆盖焊盘的丝印删除:

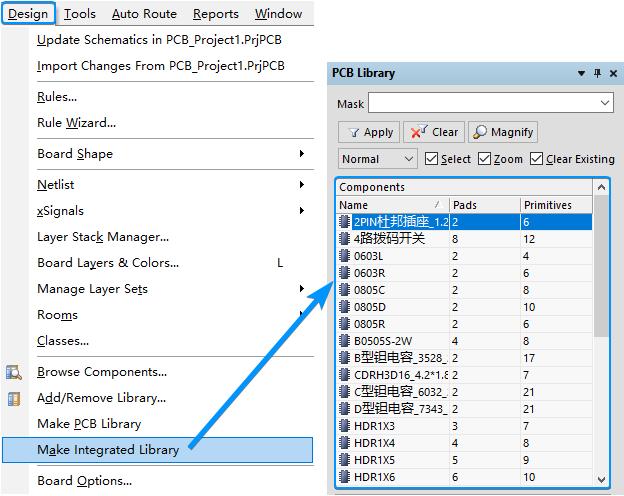

从 PCB 文件导出封装

生产环境下有时需要从已经设计完成的 PCB 文件中导出某些元件的封装,设计人员可以在打开该 PCB 文件以后,执行菜单命令 Design -> Make PCB Library或按下快捷键【D + P】,即可自动开始封装库的导出工作:

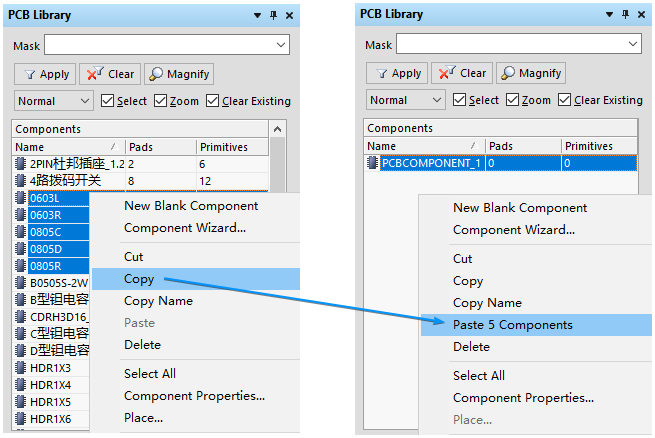

复制 PCB 封装

可以将多个 PCB

封装库里所需的封装复制至一个封装库,以便于管理与使用。首先选择 PCB

封装编辑界面右下角的 PCB -> PCB Library

调出PCB Library工作面板,并在封装列表当中按住【Shift】键逐个选中待复制的元件封装,然后鼠标右键执行Copy命令或按下快捷键【Ctrl

+

C】,最后切换至目标封装库的封装列表当中,单击鼠标右键执行Paste N Components或按下快捷键【Ctrl

+ V】粘贴封装:

封装规则检查

Altium Designer 还提供有 PCB

封装的规则检查功能,可以在创建完封装以后单击菜单栏的 Reports

-> Component Rule Check

,然后在弹出的Component Rule Check界面选择想要执行的检查任务:

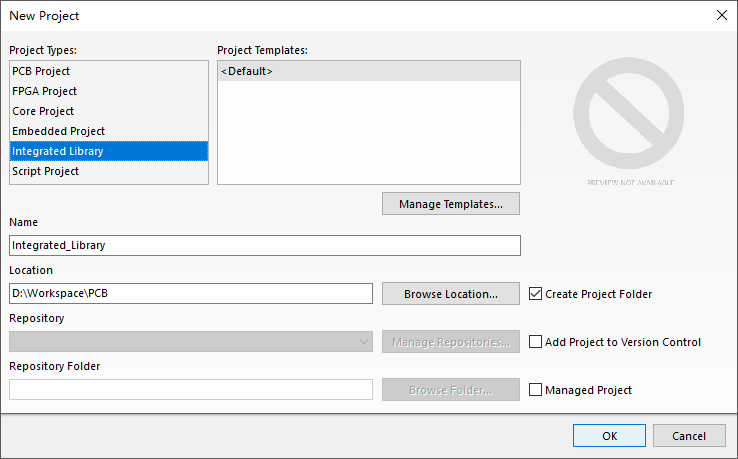

集成库

集成库(Integrated Library)整合了原理图元件、PCB

封装、仿真模型、信号完整性模型、3D

模型,便于分发共享以及快速使用。执行菜单栏命令 File -> New

-> Project -> Integrated Library

可以新建一个集成库工程Integrated_Library.LibPkg:

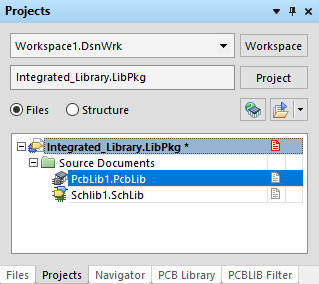

在左侧工程面板鼠标选中该集成库工程,然后右键选择 Add New to

Project -> Schematic Library 和 Add New to Project

-> PCB Library

分别创建原理图元件库Schlib1.SchLib和 PCB

封装库PcbLib1.PcbLib,

按照之前内容提到的方式,分别创建原理图元件库与 PCB

封装库,然后在原理图元件的模型管理界面添加 PCB

封装信息,从而建立两者的关联。添加完成以后,在工程名称上鼠标右键执行

Compile Integrated Library Integrated_Library.LibPkg

命令对集成库进行编译,编译完成后就会自动在工程目录下生成一个名为Integrated_Library.IntLib集成库文件。

1 | D:\Workspace\PCB\Integrated_Library |

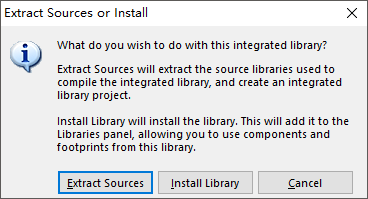

分离集成库

如果需要将给定集成库里内置的原理图元件库与 PCB

封装库进行分离,可以双击上面编译生成的集成库文件Integrated_Library.IntLib,此时会自动打开

Altium Designer 并且弹出 Extract Sources or Install

对话框:

按下【Extract

Sources】按钮即可将集成库分离为PcbLib1.PcbLib和Schlib1.SchLib两个文件。

安装与卸载

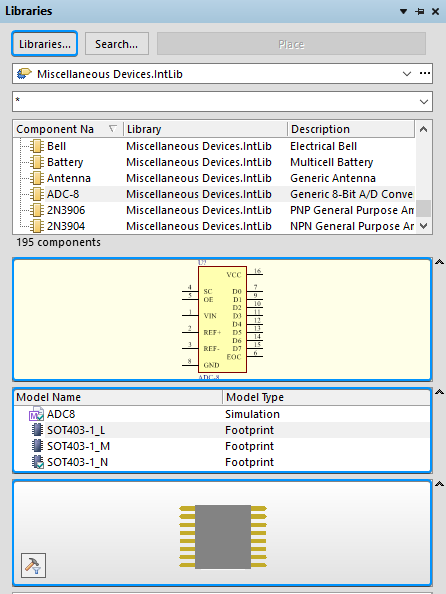

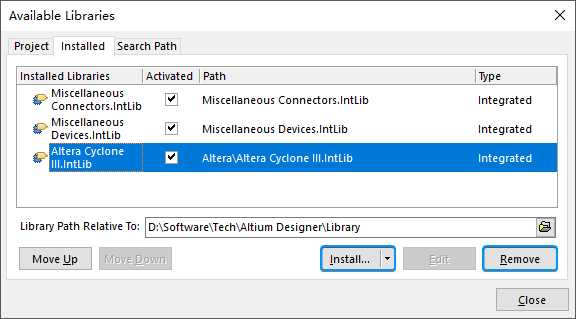

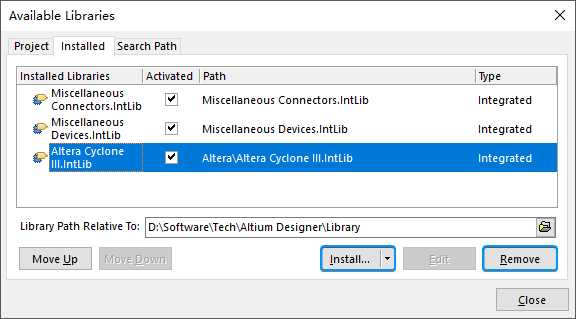

选择 Altium Designer 右侧的【Libraries】选项卡,展开库管理面板可以看到当前可供使用的集成库列表,同时还可以预览集成库中所包含的原理图元件以及对应 PCB 封装。

如果需要安装集成库,则可以点击顶部的【Libraries...】按钮,打开下面的 Available Libraries 对话框,设计人员按下该界面上的【Add Library】或【Remove】按钮,就可以方便的安装或者移除各种库文件。

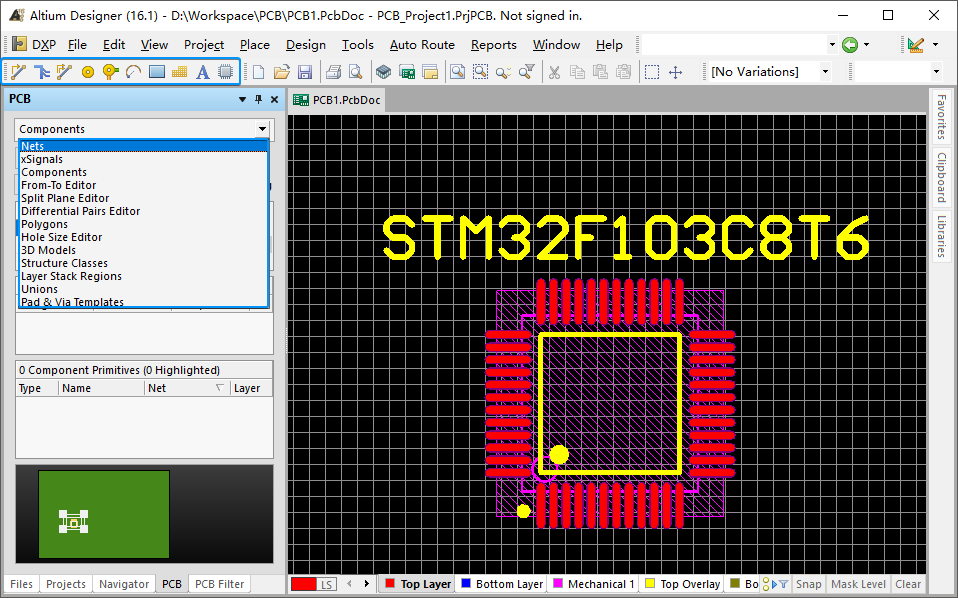

PCB 工作环境

进入 PCB 编辑器以后点击左侧面板底部的【PCB】选项卡或者底部状态栏左侧的【PCB】图标,就可以展开如下图所示的 PCB 编辑面板:

通过走线、覆铜、放置填充等操作可以实现各种电气属性的连接,Altium Designer 提供了丰富的电气连接放置命令:

| 符号 | 作用 | 符号 | 作用 |

|---|---|---|---|

|

交互式布线连接(Interactively Route Connections) |

|

按边缘放置圆弧(Place Arc by Edge) |

|

交互式布多根线连接(Interactively Route Multiple Connections) |

|

放置填充(Place Fill) |

|

交互式布差分对连接(Interactively Route Differential Pair Connections) |

|

放置多边形平面(Place Polygon Plane) |

|

放置焊盘(Place Pad) |

|

放置字符串(Place String) |

|

放置过孔(Place Via) |

|

放置元件(Paste Component) |

Altium Designer 默认提供了诸多由操作的英文首字母所触发的快捷键,下面的表格列出了 PCB 编辑器界面下较为常用的一些快捷键:

| 快捷键 | 功能描述 | 快捷键 | 功能描述 |

|---|---|---|---|

| L | 打开工作层视图设置,如果是在元件移动状态按下【L】键可以更换元件所要放置的层; | S | 打开选择菜单,例如:S + L线选、S + I框选、S + E滑动选择; |

| J | 打开跳转菜单,例如:J + C跳转至元件、J + N跳转至网络; |

Q | 切换 PCB 编辑区采用的单位(mil/mm); |

| Delete | 删除 PCB 编辑区当前选中的对象; | Page Up / Page Down | 放大或者缩小,按下鼠标中键前后推动也可完成该操作; |

| E + D | 通过鼠标点击完成 PCB 编辑区对象的删除; | A + T | 向上对齐,同理A + L向左对齐、A + R向右对齐、A + B向下对齐; |

| Shift + S | 切换 PCB 编辑区单层或多层显示; | Ctrl + M | 测量 PCB 编辑区两个对象间的距离; |

| Space | 空格键,翻转显示当前选中的对象(包括导线、过孔等); | Tab | 修改当前所放置对象的属性(如导线长度、过孔大小等); |

| Shift + Space | 改走线模式; | P + S | 放置字符串; |

| Shift + W | 选择线宽; | Shift + V | 选择过孔; |

| T + T + M | 不可更改间距的等间距走线; | P + M | 可更改间距的等间距走线; |

| Shift + G | 鼠标走线时显示当前走线的长度; | Shift + H | 显示或者关闭坐标信息显示; |

| Shift + M | 显示或关闭放大镜; | **Shift + A** | 局部自动走线; |

PCB 导入与定义

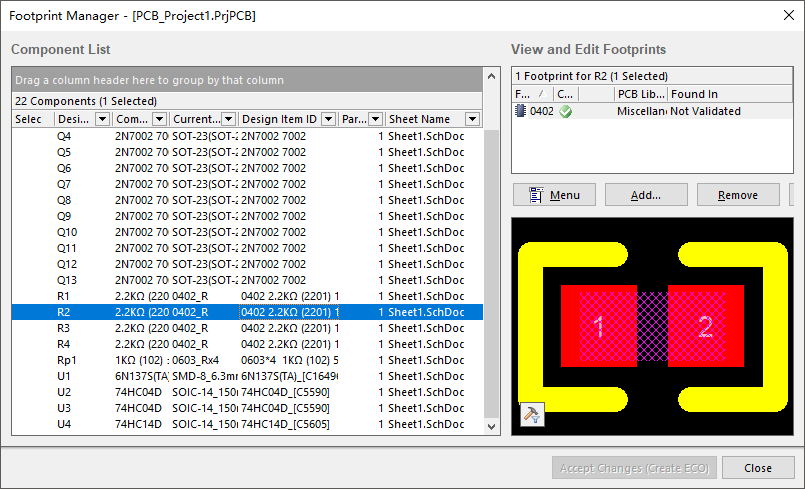

进行电路原理图转换为 PCB 的操作之前,需要使用 Altium Designer 提供的封装管理器检查原理图封装的完整性,确保原理图上的所有元件都存在对应的封装模型,避免导入出现遗漏与错误。选择菜单栏上的 Tools -> Footprint Manager... 或者按下【D + G】快捷键打开封装管理器,就可以查看并管理当前原理图元件的封装信息:

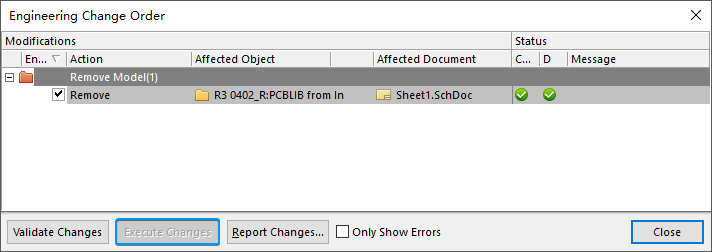

如果对元件的封装进行了编辑,那么需要按下对话框右下角的【Accept Changes(Create ECO)】按钮,然后在弹出的 Engineering Change Order 界面继续点击【Execute Changes】按钮更新封装信息:

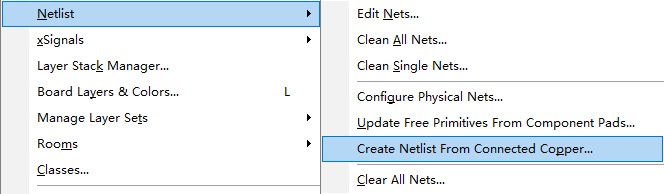

网络列表 Netlist

网络列表 Netlist 用于体现原理图上的元件及其连接关系,在 PCB

编辑界面下,执行菜单命令 Design -> Netlist -> Create

Netlist From Connected Copper...

可以导出一个针对当前工程的.Net网表文件。

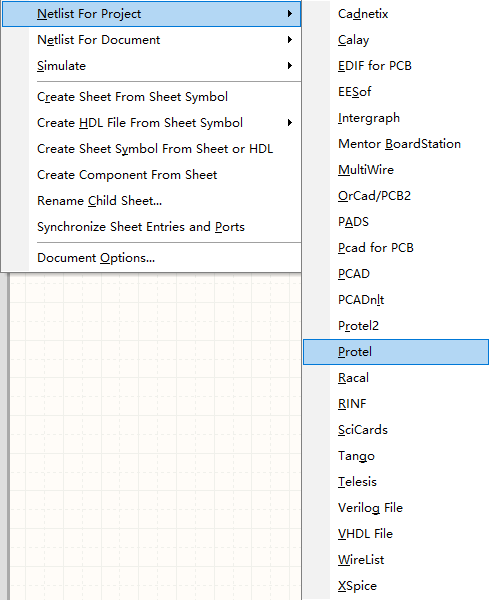

或者是在原理图编辑界面下,执行菜单命令 Design -> Netlist

For Project ->

Protel,从而在当前工程的Generated目录下生成一个针对当前原理图的.Net网表文件。

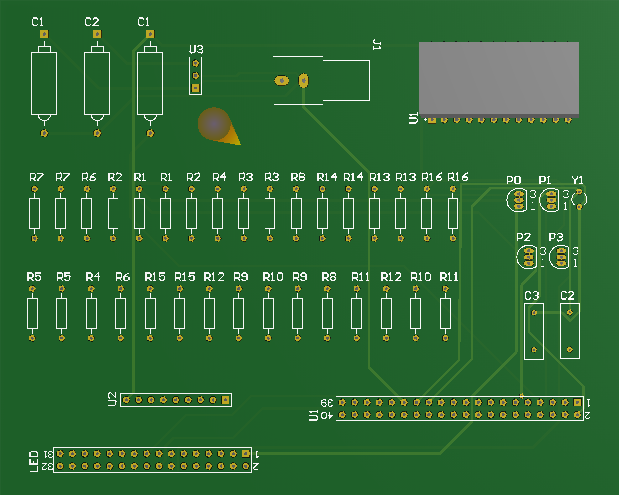

直接导入 PCB

在原理图编辑界面选择菜单 Design -> Update PCB Document PCB1.PcbDoc 或者在 PCB 设计交互界面点击菜单 Design -> Import Changes From PCB1.PrjPCB 就可以将原理图导入至 PCB,执行导入操作之后,界面会跳转至封装管理器,点击【Execute Change】按钮就可以完成导入操作:

注意:导入之前需要创建好相关工程,

Free Document类型的原理图无法进行导入。

网表对比导入

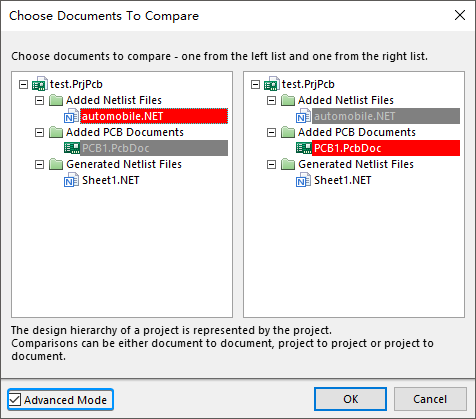

工程目录上鼠标右键,执行命令 Add Existing to Project...,将待导入的网表添加至当前工程,然后鼠标选中网表并且右键选择 Show Differences... 进入如下的网表对比窗口:

在弹出的 Choose Documents To Compare 对话框上勾选【Advanced Mode】,界面左侧选择等待导入 PCB 的网表,右侧选择网表所要更新的 PCB,最后鼠标点击【OK】按钮。

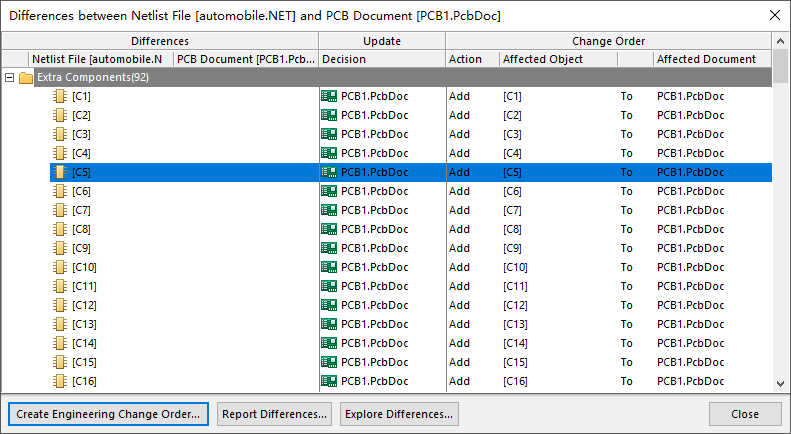

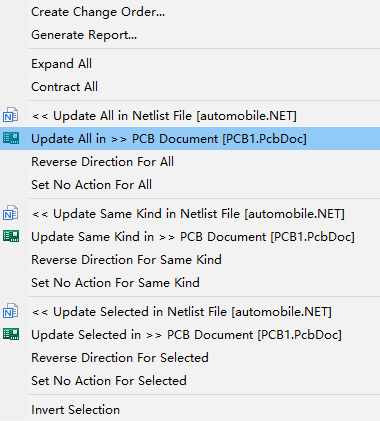

此时进入 Differences between Netlist File 网表文件比较界面,鼠标右键选择 Update All in >> PCB Document[PCB1.PcbDoc] 选项:

按下底部的【Create Engineering Change Order】按钮进入 Engineering Change Order 对话框,点击【Execute Changes】按钮,将网络列表与当前 PCB 的比较结果导入至 PCB 当中:

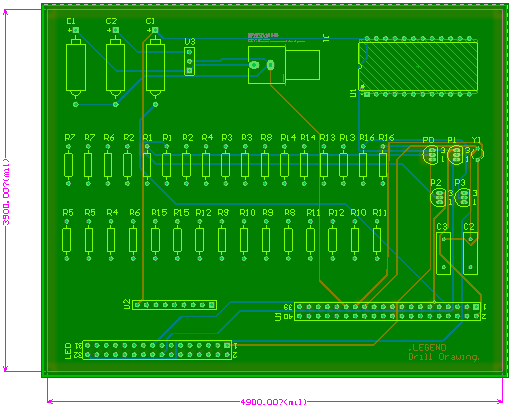

板框绘制

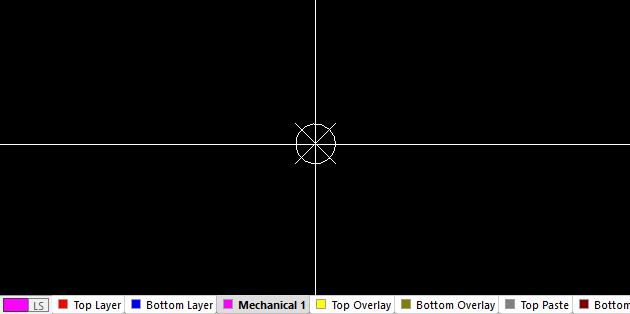

对于较为简单的圆形或矩形的 PCB 板框,可以直接在机械层或禁止布线层放置 2D 线进行绘制。接下来通过一个实例进行说明,首先将当前层切换至 Mechanical 1 层,按下快捷键【E + O + S】在指定位置放置 PCB 原点。

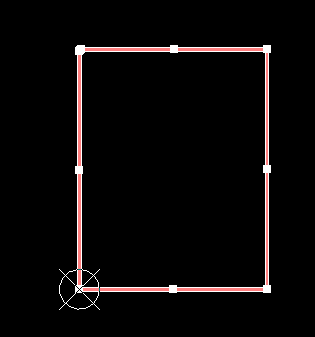

执行菜单命令 Place Line 单击原点位置放置 2D 线条,按下空格键可以调整线条的放置方向,然后双击线条调整其长度尺寸,然后修改线条的起始与末端坐标精准定义其长度,并最终绘制出一个封闭的板框区域。

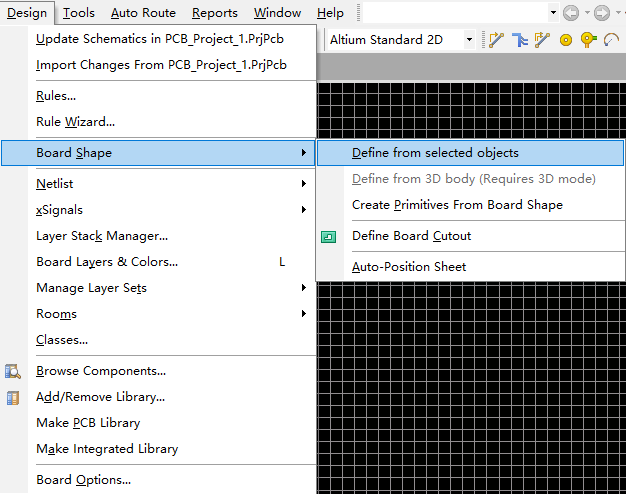

选中所绘制的闭合的板框(一定是闭合的,不然会定义不成功),执行菜单命令 Design -> Board Shape -> Define from selected objects,即可完成板框的定义。

最终得到的手绘板框效果图如下所示:

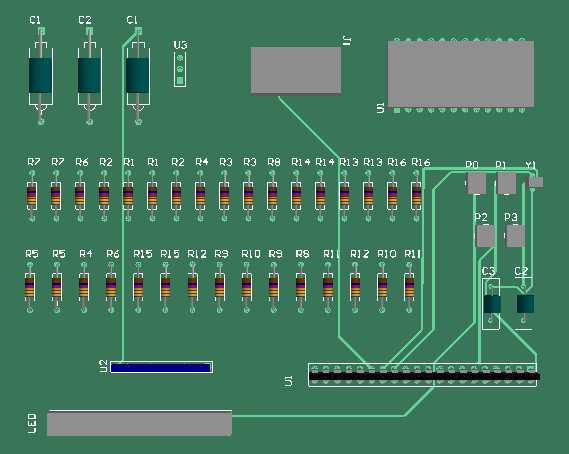

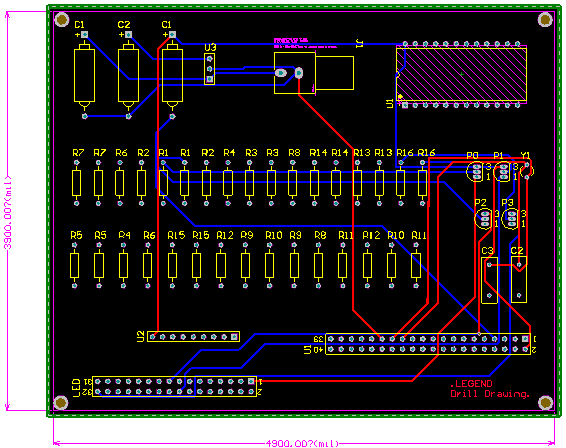

PCB 布局

优秀的 PCB 设计,除了实现电路原理功能以外,还需要考虑到 MC(电磁兼容性)、ESD(静电释放)、SI(信号完整性)等电气特性,并且兼顾机械结构、元件散热、布局美观等方面的问题。

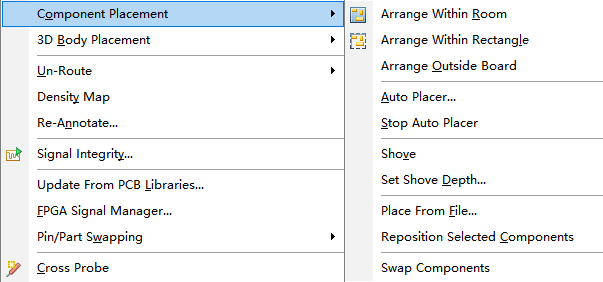

自动布局

Altium Designer 提供了强大的 PCB 自动布局功能,基于一套预置算法自动将元器件分开并放置到规划区域,点击菜单栏上的 Tools -> Component Placement或者按下快捷键【T + O】,可以打开自动布局的相关菜单项:

- Arrange Within Room:在 Room 内部排列,用于在指定的空间内部排列元件;执行后光标变为十字形状,单击需要排列元件的 Room 区域,元件就会自动排列至该 Room 内部。

- Arrange Within Reactangle:在矩形区域内部排列,用于将选中的元件排列至一个矩形区域内;使用之前需要先选中元件,待光标变为十字形状时,鼠标单击并且拖动出一个矩形区域,完成以后就会自动将元件排列至该区域当中。

- Arrange Outside Board:用于将选中的元件排列至 PCB 板的外部,使用前同样需要先选中元件,执行后就会自动将选择的元件排列至 PCB 范围之外的左上角区域。

- Auto Placer...:自动布局命令,用于执行自动布局操作。

- Stop Auto Placer:停止自动布局命令,用于停止自动布局操作。

- Shove:用于推挤布局,将重叠在一起的元件推开;选择一个元件作为基准,当周围元件与基准元件存在重叠时,则以基准元件为中心向四周推挤其他的元件;如果不存在重叠则不会执行推挤命令。

- Set Shove

Depth...:用于设置推挤命令的深度,可以是

1 ~ 1000之间的任意数字。 - Place From File...:依据导入的自动布局文件进行放置。

- Reposition Selected Components:重新放置当前选中的 PCB 元件。

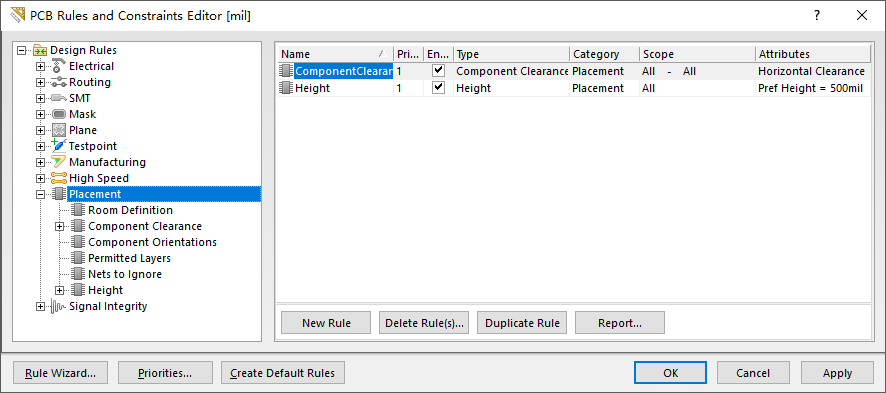

进行自动布局之前,可以设置自动布局的约束参数,从而使结果更加完善,减少后续自动布局的工作量。选择主菜单上的Design

-> Rules或者按下快捷键【D + R】,可以打开 PCB

约束和规则编辑器PCB Rules and Constraints Editor:

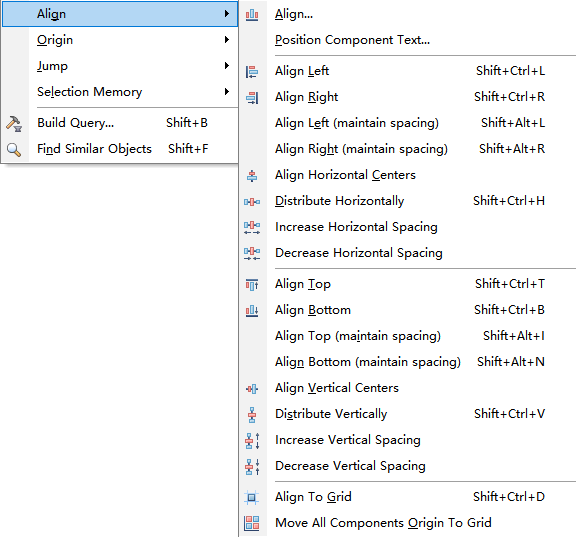

手动布局

自动布局仅仅只能对元件进行初步的摆放,需要手动进行进一步的调整,因此 Altium Designer 提供了专门的手动布局操作。其中,元件的对齐操作可以让 PCB 布局更加整齐与对称,同时也更加便于布线;点击菜单栏上的 Edit -> Align 或者按下快捷键【E + G】即可展开对齐操作相关的菜单:

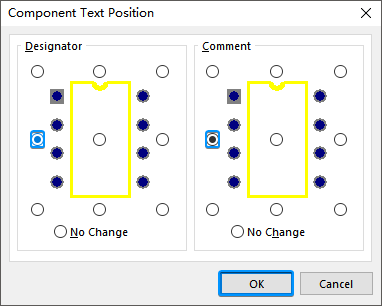

与此同时,PCB 上元件的标志符和注释的位置都是可以进行修改的,选择菜单 Edit -> Align -> Position Component Text... 或者按下快捷键【E + G + P】打开元件位置调整对话框:

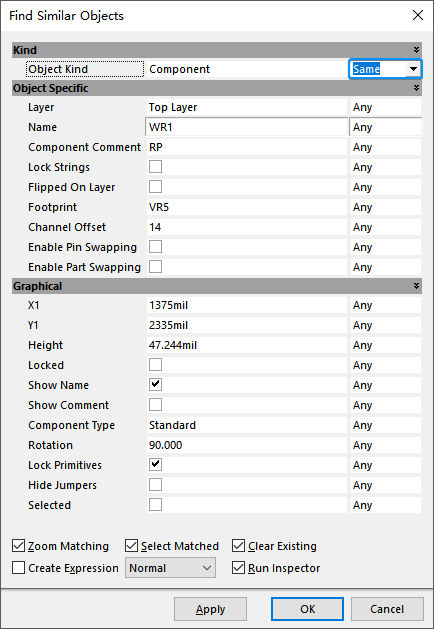

手动布局时,拖动元件时按下【空格键】可以调整元件的摆放方向。而对于需要调整多个相同类型元件的情况,可以借助查找相似命令的方式:选择菜单栏命令

Edit -> Find Similar Objects 或者按下快捷键【Shift +

F】,当光标变为十字形状时,选取 PCB

区域内的一个电子元件,此时会弹出Find Similar Objects对话框:

将Object Kinds对应的选项设置为Same,然后依次点击【Apply】和【OK】按钮,对话框关闭以后所有满足相似条件的元件都将会被选中。此时再通过对齐等操作,将各个元件排列整齐。如果发现之前定义的

PCB 形状偏大或者偏小,则还需要对 PCB 的尺寸重新进行定义。

原理图与 PCB 交互设计

PCB 绘制时,为了便于与原理图进行对应,让两者互相进行映射,需要使用到 Altium Designer 提供的交互式选择模式,从而方便快速的定位元件,缩短设计周期,提高工作效率。鼠标选择菜单栏上的 Tools -> Cross Select Mode 激活交互式选择模式:

从上面的截图当中可以看到,当选中原理图上的某个元件以后,PCB 上对应的元件就会自动同步选中,反之亦是成立的。

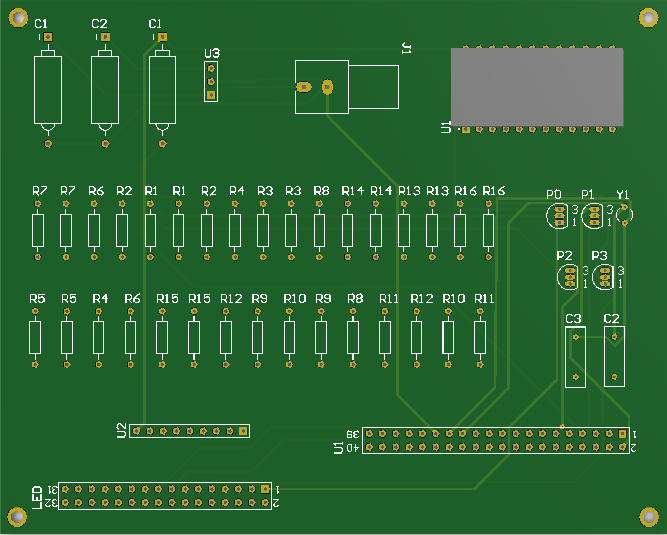

3D 预览

PCB 布局完成之后,可以通过直观查看成品的 3D 效果,来检查当前布局是否合理;选择菜单栏上的 View -> 3D Layout Mode 查看 PCB 裸板的 3D 实物效果图:

或者选择菜单栏上的 Tools -> Legacy Tools -> Legacy 3D View 查看带元件的 3D 效果:

网络密度分析

网络密度分析是利用 Altium Designer 提供的密度分析工具,对当前 PCB 文件的元件放置和连接情况进行分析,并最终生成一个临时的密度指示图(Density Map)覆盖在 PCB 上面。按下菜单栏的 Tools -> Density Map 开始进行密度分析,或者选择 Tools -> Clear Density Map 取消当前密度结果的显示。

其中绿色部分表示密度较低,红色则表示网络密度较高的区域,元件越密集连线越多的区域颜色就会呈现一定变化趋势。密度指示图展示了当前 PCB 电路板的布局密度特征,可以作为各个区域内布线难度、布通率的提示信息,从而进行相应的调整,提高后续布线的布通率,降低布线难度。

PCB 布线

PCB 上元件的布局完成之后,就可以开始进行布线操作。布线是整个 PCB 设计流程当中要求最高、细节最多、工作量最大的步骤。PCB 布线的首要任务是通过导线建立完整的电气连接,走线长度尽量短和直,以保证信号完整性;走线中尽量减少过孔的使用,并且尽量加大走线的宽度;同时输入输出导线应当避免相邻平行,从而规避反射干扰,且必要时应当增加地线进行隔离;此外,两条相邻的布线尽量互相垂直,如果平行则会导致耦合。

自动布线

对于散热、电磁干扰、高频特性要求较低的电路设计,可以采用自动布线操作来降低工作量。

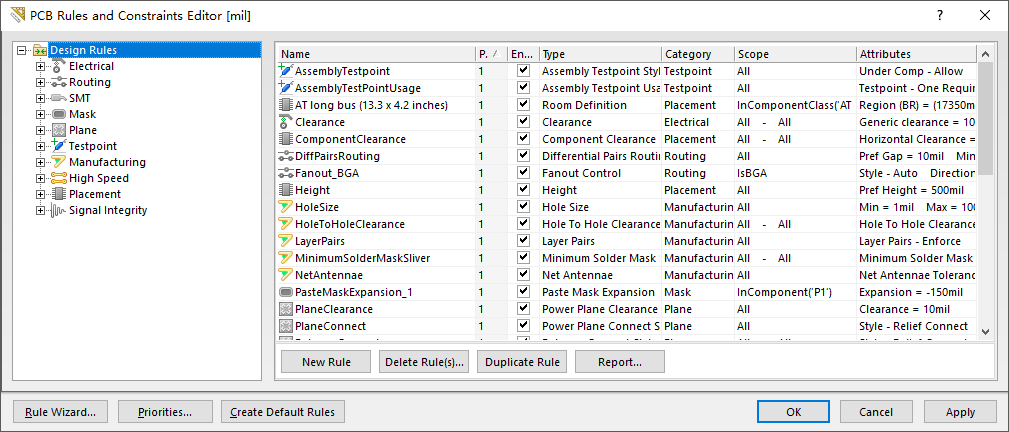

自动布线规则与约束

Altium Designer 17 在 PCB 规则和约束编辑器当中提供了 10 种设计规则,覆盖了元件的电气特性、走线宽度、走线拓扑结构、表面安装焊盘、阻焊层、电源层、测试点、电路板制作、元件布局、信号完整性等设计过程当中的方方面面。进行自动布线操作之前,需要首先对规则进行详细的设置。鼠标打开菜单栏上的 Design -> Rules... 或者按下快捷键【D + R】即可打开如下编辑界面:

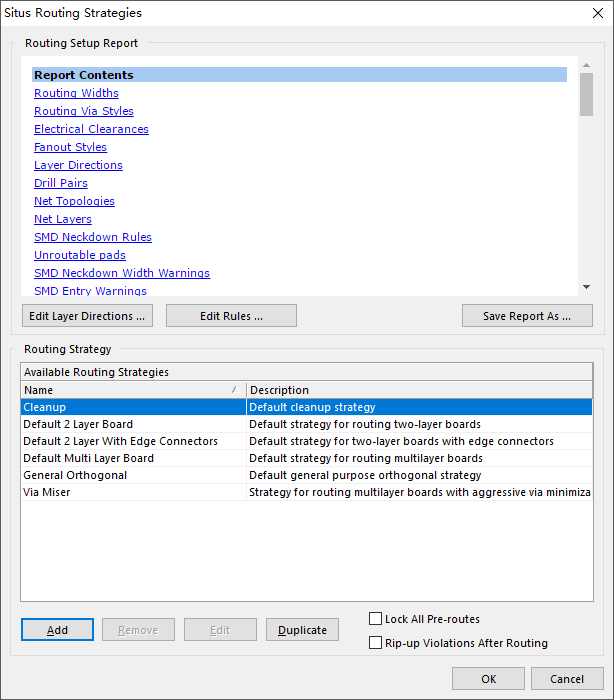

自动布线策略

布线策略是指 PCB 进行自动布线时所采取的策略,选择菜单栏上的 Route -> Auto Route -> Setup... 可以打开 Situs 布线策略对话框界面:

Situs 布线策略界面当中默认提供了如下 5 种自动布线策略:

- Cleanup:清除策略;

- Default 2 Layer Board:默认的双面 PCB 布线策略;

- Default 2 Layer With Edge Connectors:默认的具有边缘连接器的双面 PCB 布线策略;

- Default Multi Layer Board:默认的多层 PCB 布线策略;

- Via Miser:尽量减少过孔使用的策略;

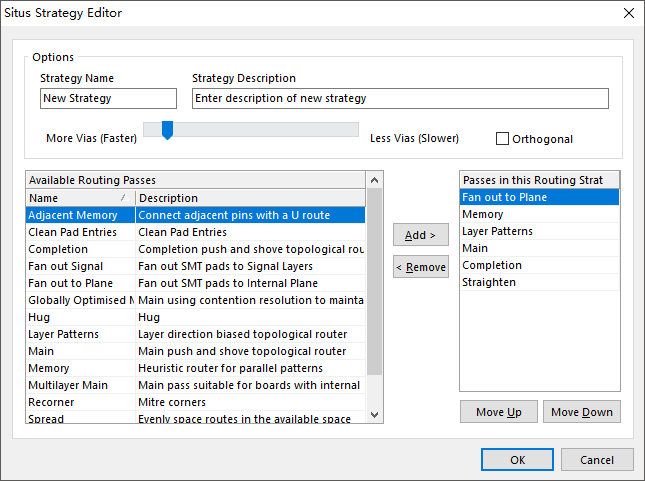

鼠标点击该界面当中的【Add】按钮可以进入 Situs 策略编辑器界面,从而自定义新的布线策略:

界面中的Strategy Name和Strategy Description分别代表自定义策略的名称与描述,下面的滑块表示该策略所允许的过孔数目(过孔越多自动布线速度越快),界面底部的左侧的列表Available Routing Passes表示已有的布线操作,右侧的Passes in this Routing Strategy则表示布线策略中的操作,可以通过中间的【Add】和【Remove】按钮添加或移除策略,或者使用下面的【Move

Up】与【Move Down】按钮调整各条策略的优先级。

自动布线操作

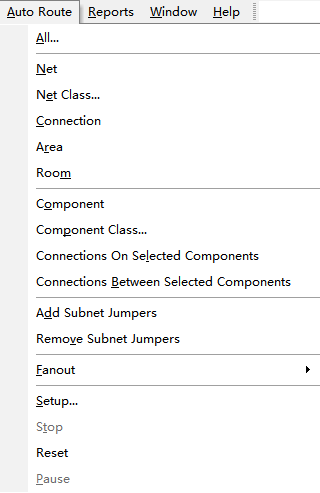

完成了布线规则与策略的设置以后,即可以开始着手自动布线操作。Altium Designer 提供的自动布线操作主要通过菜单栏上的 Auto Route 来提供,设计人员不仅可以整体进行布线,还可以对指定区域、网络、元件进行单独布线。

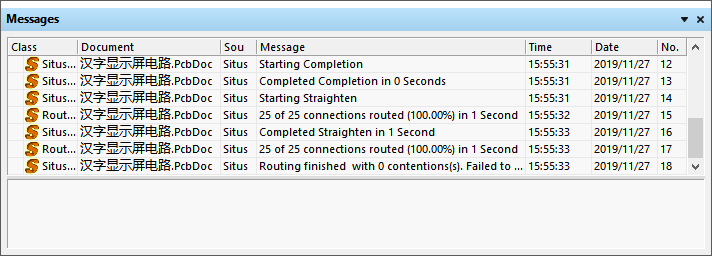

选择菜单栏上的 Auto Route -> All... 命令,进入

Situs

布线策略界面,选择默认的Default 2 Layer Board策略,最后按下【Route

All】按钮弹出一个用于提供布线状态信息的 Messages

对话框:

关闭对话框后,就可以看到自动布线的结果。当 PCB 上元件排列比较密集或者布线规则设置较为严格时,自动布线可能无法完全布通,即使布通也可能存在大量走线不合理(绕线过多、走线过长等等)的情况,此时就需要手动完成进一步的调整。

手动布线

对于自动布线中出现的一些不合理情况,可以通过手动布线进行修正。当然,对于元件较少的

PCB

设计也可以完全采用手动布线。手动布线时,由于需要设计人员自行规划元件的走线布局与路径,而网格是尺寸控制的重要依据,因此合理的设置网格尺寸,可以方便设计者规划布局与走线。设计人员在不同阶段会需要动态的调整网格的大小,例如元件布局阶段,可以将捕获网格设置大一些(例如20mil),而布线阶段则捕获网格会被设置得小一些(例如5mil),尤其是走线密集的区域,捕获网格设置小一些便于观察与走线。

拆除布线

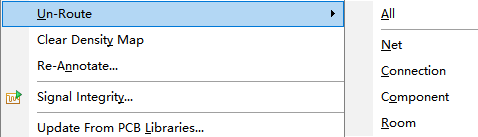

如果需要删除自动布线时遗留下的一些不合理走线,直接按下键盘上的【Delete】就可以完成。当删除工作量较大的时候,可以选择菜单栏上的 Tools -> Un Route 或者按下快捷键【T + U】,选择子菜单里相应的删除方式快速拆除布线。

- All:拆除当前 PCB 上所有布线;

- Net:拆除指定网络上的布线;

- Connection:拆除鼠标指定连接上的布线;

- Component:拆除指定元件上的布线;

- Room:拆除指定 Room 区域内的布线;

手动布线操作

手动布线遵循与自动布线相同的约束与规则,其具体操作步骤如下:

- 执行菜单栏命令 Place -> Interactive Routing,鼠标光标此时变为十字形状;

- 移动光标到 PCB 元件的焊盘上,点击放置布线的起点;

- 选择另一个焊盘,点击放置布线的终点;

手动布线模式下可以通过【Shift + Space】切换转角的角度模式,可以选择任意角度、40° 或 90° 的矩形拐角、45° 或 90° 的弧形拐角共五种。

注意:交互式布线时,按下小键盘区的【 * 】键可以在不同信号层之间切换,从而方便的完成不同信号层上的走线。此外,对于不同 PCB 层上的走线,Altium Designer 会自动为其添加一个过孔进行连接。

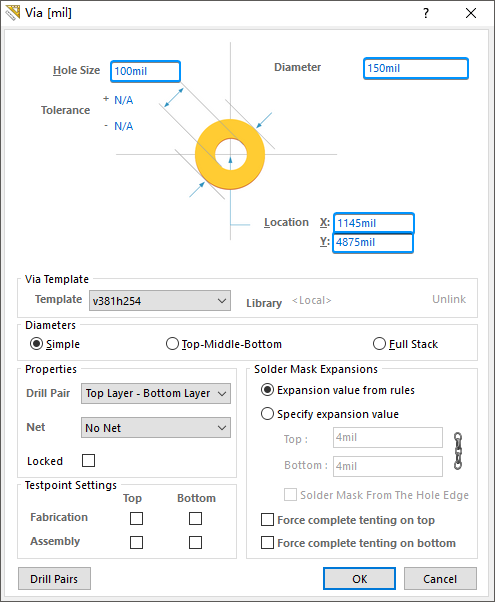

安装孔

电路板布线完成之后,就可以开始着手添加 PCB 上的安装孔;安装孔通常采用过孔形式,并与接地网络进行连接,以方便后期调试。选择菜单栏 Place -> Via 放置过孔,然后按下【Tab】键打开过孔属性设置界面:

Hole Size孔尺寸选项,由于这里过孔是作为安装孔使用,所以需要设置一个较大的内径,这里填写100mil;Diameter直径选项,用于设置过孔的外径,此处填写为150mil;Location位置项,通常设置到

PCB 的四个角上面。下图是一块已经完成了安装孔放置的 PCB 设计:

覆铜操作

覆铜用于填充 PCB 上的不规则区域,并与电路网络进行连接,通常情况是直接连接至 GND。覆铜工艺可以提高电路的抗干扰能力,并增强大电流的通过能力,因此其安全间距应是普通导线的 2 倍以上。

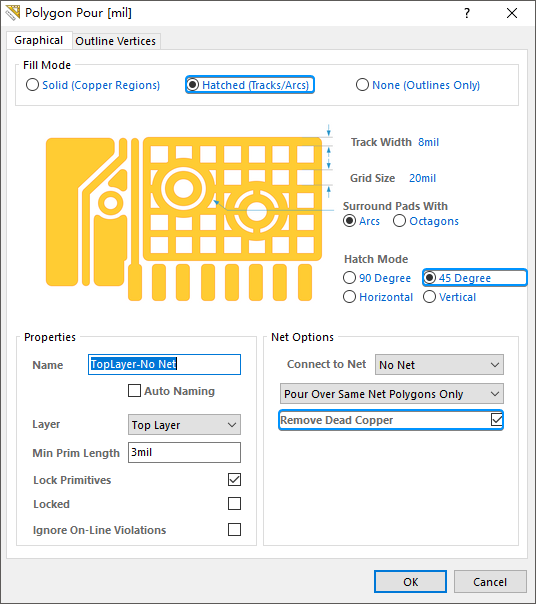

鼠标选中菜单栏上的 Place -> Polygon Pour... 或者按下快捷键【P + G】,Altium Designer 将会弹出多边形覆铜对话框:

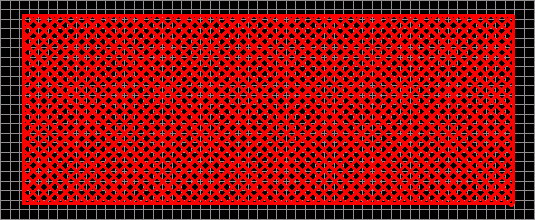

顶部Fill Mode单选按钮组里面,Solid(Copper Regions)是指覆盖区域为全铜敷设,Hatched(Tracks/Arcs)是指向覆盖区域填充网络状的铜层,None(Outlines Only)则只保留覆铜边界,内部不进行填充处理。这里我们选择网状铜层,孵化铜层为45°,链接至GND,并作用于Top Layer,最后选中移除死铜,按下【OK】按钮以后,光标变为十字形状时,在禁止布线层

Keep Out 拖拽出一个矩形框,此时 Altium Designer

就会自动在 PCB 顶层填充出一个网状的铜层:

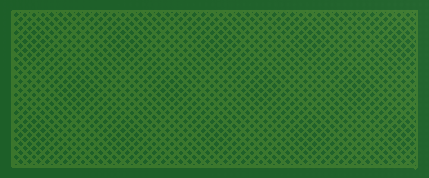

打开 PCB 的 3D 预览功能,可以看到该铜层最终所呈现的效果:

注意:以同样的方式,还可以选择在 PCB 的底层

Bottom Layer进行覆铜操作。

补泪滴

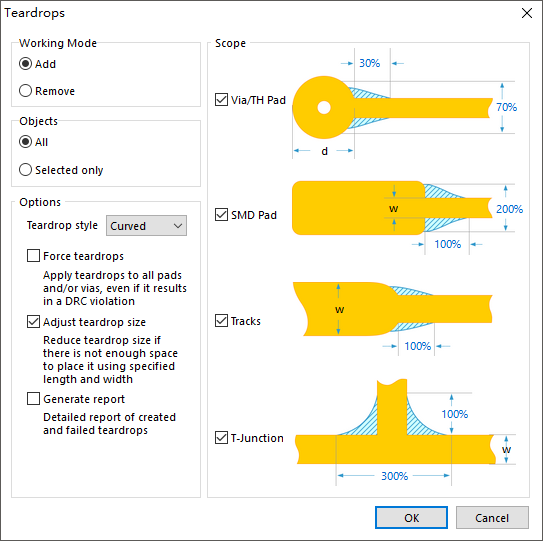

PCB 导线与焊盘、过孔的连接位置,通常需要进行补泪滴操作,去除连接处直角的同时,增大连接面。一方面避免 PCB 加工过程中,因为钻孔偏差导致焊盘与导线断裂;另一方面是在安装和使用过程中,避免受力不均衡导致断开。

鼠标点击菜单栏上的 Tools -> Teardrops 命令或者按下【T + E】快捷键即可开始进行补泪滴操作,此时 Altium Designer 会弹出泪滴属性的设置界面:

其中,工作模式选项Working Mode用于表明当前操作是需要Add添加还是Remove删除泪滴,对象选项Objects表示需要添加泪滴的是所有All还是仅仅是选中的对象Selected Only。复选框Force teardrops强制对所有焊盘或者过孔添加泪滴,取消选中则在安全间距过小的时候不自动添加泪滴;复选框Adjust teardrop size用于自动调整泪滴的大小;复选框Generate report则用于生成泪滴相关的报表文件。此外,泪滴类型Teardrop style下拉菜单里拥有Curved曲线(上图)和Line线(下图)两种泪滴类型:

SPICE 电路仿真

SPICE是以集成电路为重点的仿真程序(Simulation Program with Integrated Circuit Emphasis)的英文缩写,Altium Designer 在原理图层面提供了完善的 SPICE 混合信号仿真功能,除提供对SPICE标准的支持以外,还支持对Pspice模型与电路进行仿真。Altium Designer 内置的集成库的原理图符号当中包含了对应的仿真模型,因此原理图可以直接用作仿真电路。

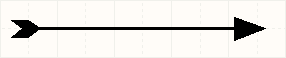

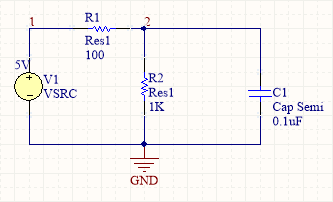

这里通过一个直流工作点分析的实例,来讲解 Altium Designer

进行原理图仿真分析的基本步骤。首先从Simulation Sources.IntLib和Miscellaneous Devices.IntLib库中找到相应元件,并绘制如下原理图:

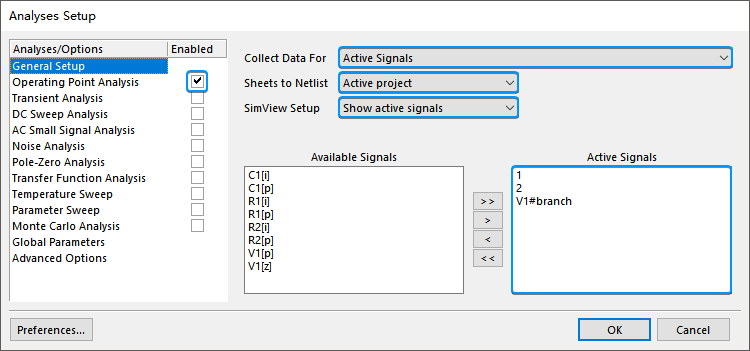

选择 Altium Designer 主菜单下的Design -> Simulate -> MixedSim,在弹出的Analyses Setup分析设置对话框进行如下设置:

点击【OK】以后,弹出 SIPCE 电路分析过程的消息窗口:

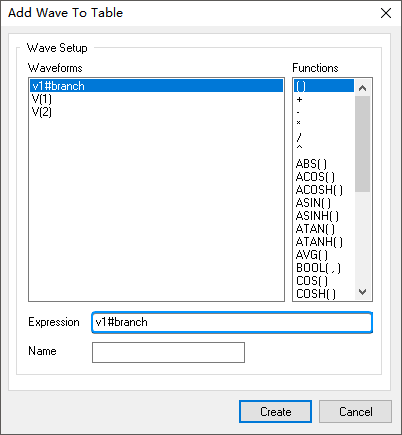

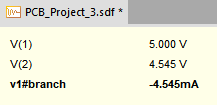

点击关闭该消息窗口,此时会自动打开PCB_Project1.sdf文件,在打开的文件上右键选择【Add

Wave】打开Add Wave To

Table对话框,添加V(1)、V(2)、v1#branch三个直流分析工作点

点击界面上的【Create】按钮,就能看到流经电阻的电流为4.545mA:

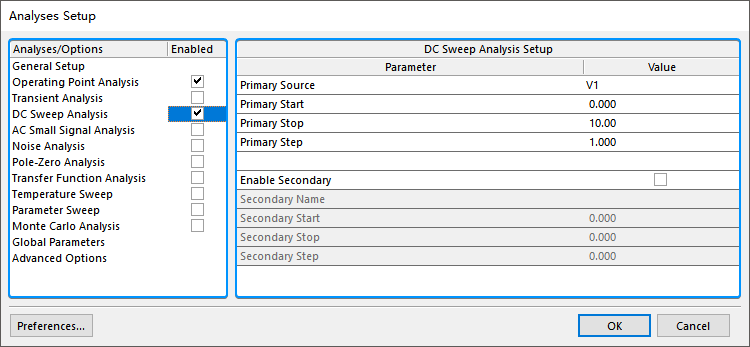

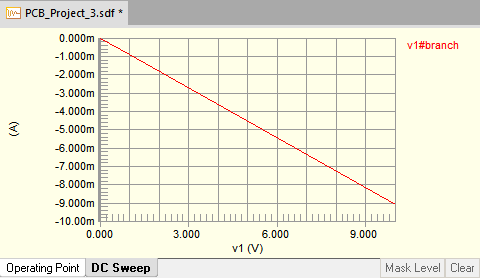

接着再次通过Design -> Simulate -> MixedSim打开Analyses Setup分析设置对话框,勾选DC Sweep Analysis选项,并进行如下设置:

点击【OK】按钮后,关闭 SIPCE

电路分析过程消息窗口,此时会自动打开PCB_Project1.sdf文件,将文件底部的选项卡从【Operating

Point】切换至【DC Sweep】:

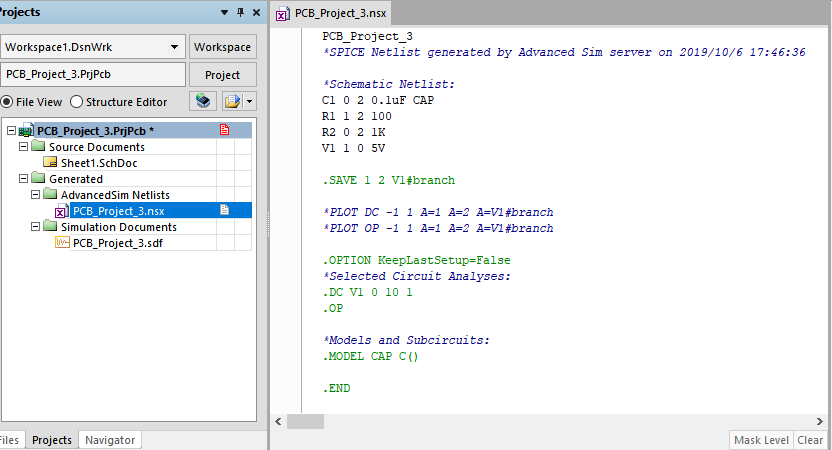

在左侧工程面板下找到当前项目的PCB_Project1.nsx文件,双击打开:

上面窗口中的代码展示了一个完整的 SPICE 分析源程序,其中第 1

行PCB_Project_1是标题行,以*号开始的是注释内容,.END用于标识结束行,.MODEL用于声明模型描述,其它.DC和.OP等以.开头的语句则用于执行相应的分析命令。

SI 信号完整性

信号完整性(SI,Signal Integrity)是指 PCB 上的信号经由信号线传输以后仍然能保持完整与正确,当电路中的信号能够以正确的时序、符合要求的持续时间与电压幅度进行传送,并完整的到达输出端时,即说明该电路具有良好的信号完整性;而当信号不能正常响应时,就认为出现了信号完整性问题,特别是在高频高速电路当中。因此,信号完整性分析的目的就是为了确保信号的时序与电压幅度正确传输,电路设计当中常见的信号完整性问题主要集中在如下几个方面:

传输延迟 Transmission Delay

指信号没有在规定的时间内以一定的持续时间和幅度到达接收端,通常是由于驱动过载、布线过长的传输线效应引起。此外,传输线上的电容、电感也会对信号的状态切换产生延时。高速电路设计当中,传输延迟是一个无法回避的问题,因此专门引入了一个延迟容限的概念,即确保电路正常工作的前提下,所允许的信号最大时序变化。

反射 Reflection

指传输线上的回波,信号功率的一部分从源端经过传输线传递至负载,另一部分则会向源端反射。高速电路设计当中,可以将导线等效为传输线,而非集总参数电路中的导线。若阻抗匹配(源端阻抗、传输线阻抗、负载阻抗三者相等)则反射不会发生;反之,如果负载阻抗与传输线阻抗不匹配就会导致接收端向源端的信号反射。

布线的几何形状、不恰当的端接方式、经过连接器的传输及电源平面不连续等因素均会导致该问题,进而导致传送信号出现严重的过冲(Overshoot)或下冲(Undershooot)现象,并最终造成信号的波形变形与时序混乱。

窜扰 Crosstalk

指没有电气连接的信号线之间的感应电压与电流所导致的电磁耦合,这种耦合会造成信号线产生类似天线的作用。其中,容性耦合会引发耦合电流,感性耦合则会引发耦合电压,并伴随时钟速率的提升与 PCB 尺寸的缩小而加大,一切都是由于信号线上有交变的信号电流通过所产生的磁场,处于该磁场中的其它信号线就会感应到信号电压。PCB 的工作层的参数、信号线间距、驱动与接收端的电气特性、信号线本身的端接方式等等都会对窜扰造成一定影响。

接地反弹 Ground Bounce

指由于电路中由于较大电流涌动而在电源与接地平面之间产生的大量噪声,例如大量芯片同步进行切换时,就会在与电源平面之间产生较大的瞬时电流,而芯片封装与电源之间的寄生电感、电容、电阻就会随之引发电源噪声,造成电路在零电位上产生较大的电压波动,进而影响其它元器件的正常工作。

Altium Designer 17 拥有完整的信号完整性仿真功能,能够分析 PCB 设计并且检查相关参数,测试整板的串扰、过冲、下冲、上升时间、下降时间、线路阻抗等问题,从而以最小代价发现当前电路设计当中所存在的问题。与电路仿真模型类似,信号完整性分析也是建立在元件的模型基础之上的,这种模型称为 Signal Integrity 模型,简称 SI 模型。元件的信号完整性 SI 模型可以在信号完整性分析之前设定,也可以在信号完整性分析进行的过程中进行设定。

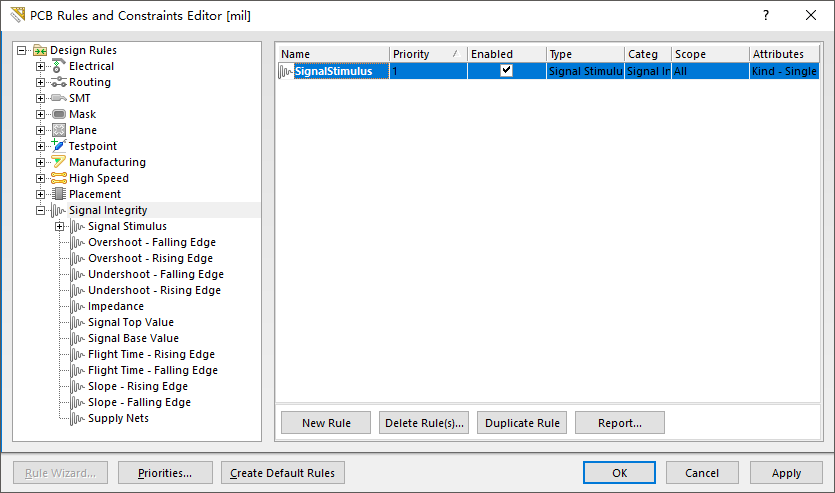

信号完整性规则设置

Altium Designer 包含有诸多信号完整性分析规则,可以通过菜单栏的

Design -> Rules... 打开 PCB

规则及约束编辑器,并且切换至如下的Signal Integrity子菜单,按下【New

Rule】按钮即可新建指定的规则或约束:

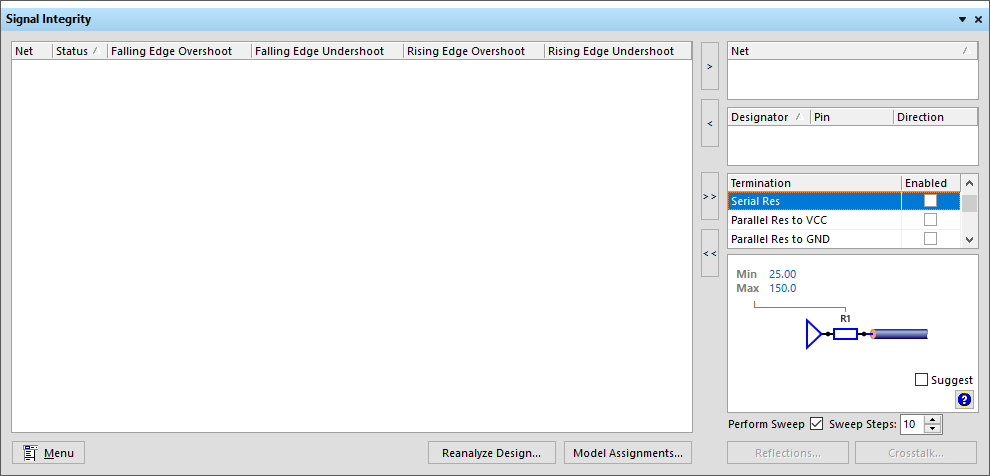

信号完整性分析操作

设置完毕信号完整性分析相关的元件 SI 模型以及规则以后,就可以开始实际的信号完整性分析操作,这项工作一般会分为 2 个步骤:首先是对目标 PCB 网络进行初步分析,了解哪个部分的 SI 特性最差;然后筛选出一些信号进行进一步的详细分析。鼠标选择菜单栏上的 Tools -> Signal Integrity 命令或者按下快捷键【T + Y + Y】即可进入信号完整性分析界面:

PCB 后期处理

PCB 的布局和布线完成以后,还需要执行 DRC 检查、导出 Geber 等进行的操作。

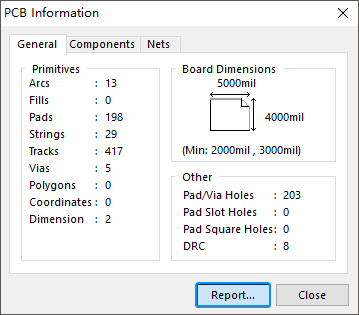

导出 PCB 信息

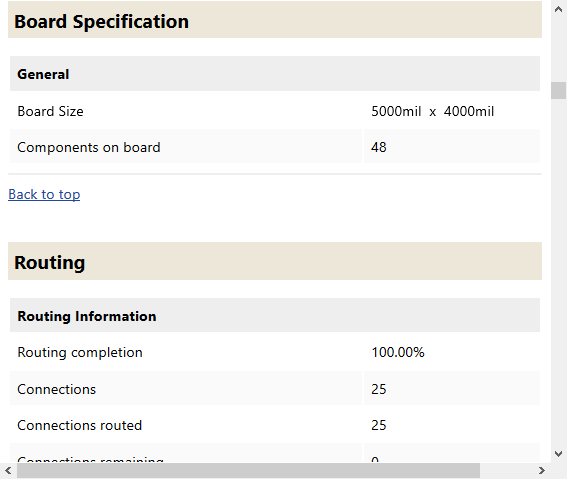

选择主菜单上的 Reports -> Board Information 进入如下的 PCB 信息对话框,上面的 3 个选项卡分别用于展示【通用】、【元件】、【网络】的信息:

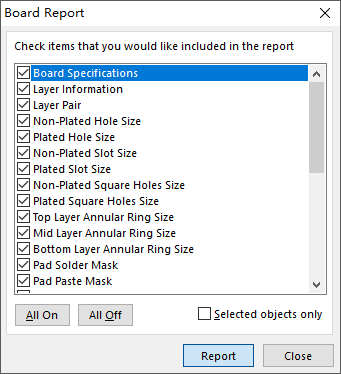

继续点击【Report...】按钮,进入 PCB 报告对话框,然后选择所需要生成的报告内容:

最后,再次点击 PCB

报告对话框上的【Report】,生成以.REP作为后缀名的报告文件并在工作区展开:

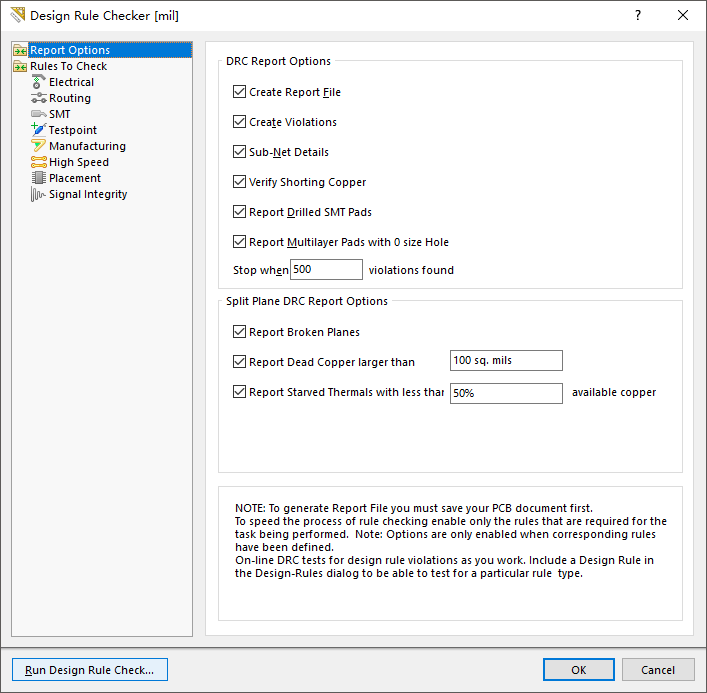

DRC 检查

PCB 设计完成之后,在正式的输出 Geber 制板文件之前,还需要进行一次完整的设计规则检查。Altium Designer 提供的设计规则检查(DRC,Design Rule Check)会基于用户设置的规则,检查当前 PCB 的导线宽度、安全距离、元件间距、过孔类型等设计。选择菜单栏上的 Tools -> Design Rule Check... 命令或者按下快捷键【T + D】,打开设计规则检查对话框:

注意:左侧列表中的

Report Options是 DRC 报告设置选项,通常保持默认即可;而Rules To Check则是待检查的 DRC 规则列表,按需勾选即可。

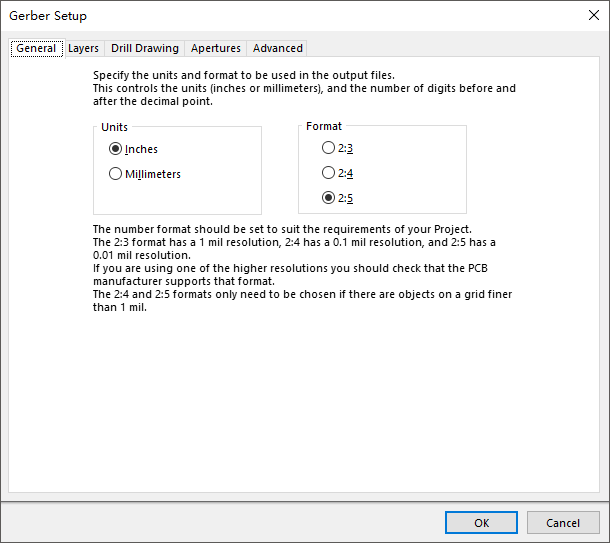

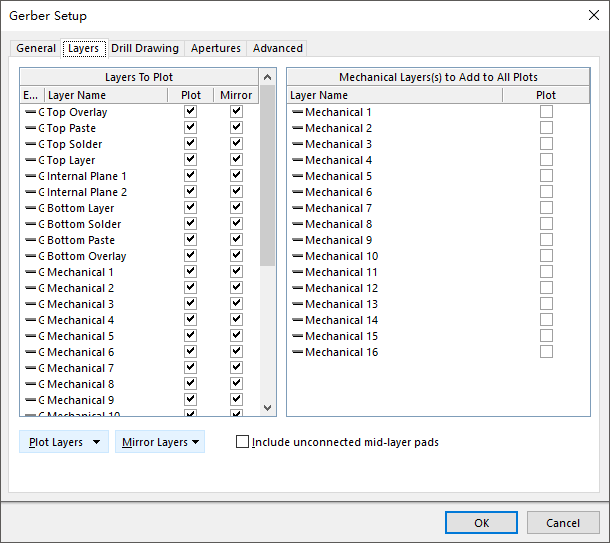

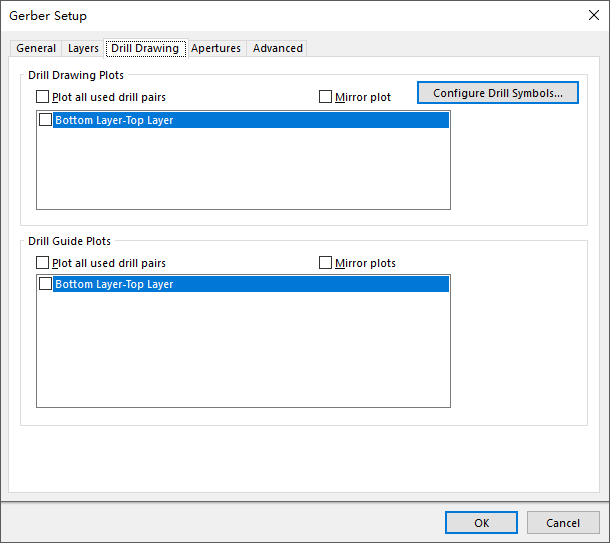

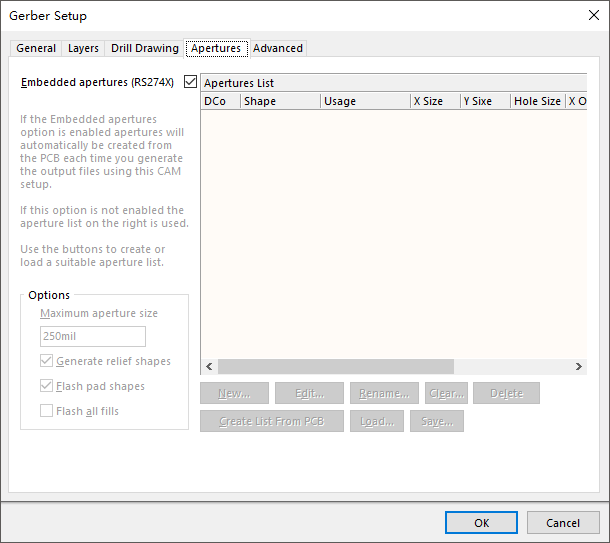

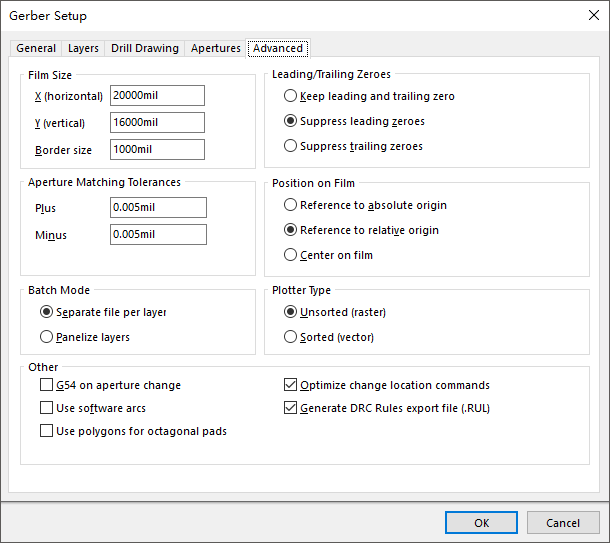

导出 Gerber

Gerber ['dʒɜ:bə] 是一种符合 EIA 电子工业协会标准,用于将 PCB 布线数据转换为光绘机可以处理的文件格式。在 PCB 编辑器界面下选择菜单栏上的 File -> Fabrication Outputs -> Gerber Files 打开如下 Gerber 设置相关的一系列对话框:

【General】通用选项卡,用于指定在输出 Gerber

文件中使用的单位与格式,其中Format栏目下的2:3、2:4、2:5分别代表的是数据精度,例如:2:3表示数据包含了

2 位整数和 3

位小数。设计者应该根据自己设计中所使用的单位精度进行选择,精度越高对于

PCB 制造的工艺要求越高。

【Layer】层选项卡,用于设置需要生成 Gerber 文件的 PCB

层。左侧的Layers To Plot列表表示需要生成 Gerber

的层,右侧的Mechanical Layers to Add to All Plots列表用于选择需要加载到各个

Gerber 层的机械层。

【Drill Drawing】层选项卡,用于对 PCB 上的钻孔对应的层进行设置。

【Apertures】光圈选项卡,用于设置生成 Gerber

文件时建立的光圈选项,这里默认选择Embedded apertures (RS274X),即生成

Gerber 时自动建立光圈。

【Advanced】高级选项卡,可以设置光绘胶片的相关选项,例如:胶片尺寸及边框大小、零字符格式、板层在胶片的位置、制造文件生成模式等等。

完成 Gereber

相关的各项设置以后,单击【OK】按钮就会开始自动生成各个图层的 Gerber

文件,并且在工程的Generated目录当中生成CAMtastic.Cam文件。Altium

Designer 17 针对不同的 PCB 层生成相应的扩展名,具体请见下表所示:

| PCB 层 | Gerber 扩展名 | PCB 层 | Gerber 扩展名 |

|---|---|---|---|

| Top Overlay | .GTO |

Top Paste Mask | .GTP |

| Bottom Overlay | .GBO |

Bottom Paste Mask | .GBP |

| Top Layer | .GTL |

Drill Drawing | .GDD |

| Bottom Layer | .GBL |

Drill Drawing Top to Mid1, Mid2... | .GD1,.GD2... |

| Mid Layer 1, 2... | .G1,.G2... |

Drill Guide | .GDG |

| PowerPlane 1, 2... | .GP1,GP2... |

Drill Guide Top to Mid1, Mid2... | .GG1,.GG2... |

| Mechanical Layer 1, 2... | .GM1,GM2... |

Pad Master Top | .GPT |

| Top Solder Mask | .GTS |

Pad Masterr Bottom | .GPB |

| Bottom Solder Mask | .GBS |

Keep-out Layer | .GKO |

运用 Altium Designer 进行 PCB 电路的绘制与仿真