Cadence SPB OrCAD/Allegro 设计技巧合集

楷登电子

推出的 Cadence SPB(SPB 是

Silicon、Package、Board

三个英文字母的缩写)整合了原理图绘制工具 OrCAD 和 PCB

版图设计工具 Allegro 以及电路仿真工具

PSpice,已经成为了业界领先的电子设计自动化(EDA,Electronic

Design

Automation)工具链。伴随电子系统复杂度的日益提升,如何运用工具当中提供的各种功能来应对设计挑战,业已成为了广大电子硬件工程师们亟需掌握的技能。

关于 OrCAD 和 Allegro

的基础操作,已经在五年之前所撰写的《写给有经验 PCB

工程师的 Cadence SPB 17.4

极速上手指南》这篇文章当中进行过图文并茂的阐述,而本文则主要聚焦于实际应用中的高频痛点,提炼出经过验证的

操作技巧 和

配置方法。希冀能够帮助广大的电子硬件工程师,更加合理与熟练的使用

Cadence SPB 工具套件进行原理图和 PCB

版图的绘制,从而有效的提高研发工作效率,进而得心应手的面对各类纷繁复杂的设计挑战。

OrCAD/Allegro 的正确打开方式

- 鼠标依次点击 OrCAD 菜单栏上的

File -> Change Product...,然后选择【OrCAD Capture CIS】; - 鼠标依次点击 Allegro 菜单栏上的

File -> Change Editor...,然后选择【Allegro PCB Designer】,并且勾选所需的功能项,例如High-Speed、PCB Team Design、Analog/RF;

Cadence SPB 工程文件常用后缀

| 文件类型 | 后缀名称 | 文件类型 | 后缀名称 | 文件类型 | 后缀名称 |

|---|---|---|---|---|---|

| Cadence 工程 | .opj |

PCB 封装 | .psm |

原理图库 | .olb |

| Logo 图形 | .osm |

PCB 封装源文件 | .dra |

无电气特性的机械零件 | .bsm |

| PCB 版图 | .brd |

原理图文件 | .dsn |

负片通孔连接方式 | .fsm |

| Cadence 网表 | .dat |

自定义焊盘图形 | .ssm |

Allegro 操作记录 | .jrl |

| 第三方网表 | .net |

焊盘 | .pad |

日志 | .log |

| 操作记录脚本 | .scr |

可重复的模块定义 | .mdd |

PCB 规则钻孔 | .drl |

| PCB 不规则钻孔 | .rou |

光绘文件 | .art |

- | - |

原理图符号和 PCB 封装的默认位置

- OrCAD

默认原理图符号库:

C:\Cadence\SPB_17.4\tools\capture\library; - Allegro 默认 PCB

封装库:

C:\Cadence\SPB_17.4\share\pcb\pcb_lib\symbols;

其中在 OrCAD 自带的原理图符号库当中,比较常用的有如下三种:

Discrete.olb原理图符号库:用于存放分立式元件;Transistor.olb原理图符号库:用于存放有各类晶体管;Connector.olb原理图符号库:用于存放有各种连接器;

OrCAD/Allegro 关闭 Start Page 页面

关闭 OrCAD 启动时自动显示【Start Page】页面的方法:

- 鼠标依次点击 OrCAD 菜单栏上的

View -> Toolbar -> Command Window; - 在底部的命令行窗口执行

SetOptionBool EnableStartPage 0之后,再按下回车键; - 重新启动 OrCAD 之后,就不会再弹出 Start Page 页面;

除此之外,更为有效的办法是直接对

C:\Cadence\Spb_data\cdssetup\OrCAD_Capture\17.4.0\Capture.ini

文件进行修改:

1 | [Preferences] |

注意:上述操作必须在完全关闭 Cadence SPB 之后进行,避免修改好的配置被覆盖丢失。除此之外,上述方法可能已经在 Cadence SPB 17.4 的 S039 版本失效,请用户酌情使用。

关闭 Allegro 启动时自动显示【Start Page】页面的方法:

- 鼠标依次点击 Allegro 菜单栏上的

Setup -> User Preferences...; - 鼠标选中弹出【User Preferences Editor】界面上的【Display】选项;

- 通过在界面底部的搜索框查找

start关键字,勾选查找结果列表中的allegro_no_startpage项即可;

【OrCAD 原理图快捷操作】

| OrCAD 快捷键 | 功能说明 | 应用环境 |

|---|---|---|

| 鼠标滚轮 | 上下移动图纸 | 【原理图】编辑器 |

| Shift + 鼠标滚轮 | 左右移动图纸 | 【原理图】编辑器 |

| Ctrl + 鼠标滚轮 | 缩放图纸 | 【原理图】编辑器 |

| B | 放置总线 | 【原理图】编辑器 |

| E | 放置总线分支入口 | 【原理图】编辑器 |

| F | 放置电源符号 | 【原理图】编辑器 |

| G | 放置 GND 符号 |

【原理图】编辑器 |

| J | 放置连接点 | 【原理图】编辑器 |

| N | 放置网络别名 | 【原理图】编辑器 |

| P | 放置元器件 | 【原理图】编辑器 |

| T | 放置文本 | 【原理图】编辑器 |

| W | 放置电气连线 | 【原理图】编辑器 |

| Y | 放置图形连线 | 【原理图】编辑器 |

| X | 放置无连接符号 | 【原理图】编辑器 |

| Ctrl + B | 跳转到前一个 Part |

【原理图符号】编辑器 |

| Ctrl + N | 跳转到后一个 Part |

【原理图符号】编辑器 |

| Ctrl + E | 编辑属性 | 【原理图 & 符号】编辑器 |

| Ctrl + F | 查找 | 【原理图 & 符号】编辑器 |

| Ctrl + T | 吸附到栅格点 | 【原理图 & 符号】编辑器 |

| Ctrl + Y | 重做 | 【原理图 & 符号】编辑器 |

| Ctrl + Z | 撤销 | 【原理图 & 符号】编辑器 |

| F4 | 重复操作 | 【原理图 & 符号】编辑器 |

| C | 以鼠标指针为中心 | 【原理图 & 符号】编辑器 |

| I | 放大 | 【原理图 & 符号】编辑器 |

| O | 缩小 | 【原理图 & 符号】编辑器 |

| R | 旋转 | 【原理图 & 符号】编辑器 |

| H | 水平镜像 | 【原理图 & 符号】编辑器 |

| V | 垂直镜像 | 【原理图 & 符号】编辑器 |

| E | 结束连线 | 【原理图 & 符号】编辑器 |

预览 OrCAD 原理图符号的封装

打开 OrCAD 的时候,界面底部的【Session Log】会打印出,当前所使用的 INI 配置文件的路径:

1 | INI File Location: C:\Cadence\Spb_data\cdssetup\OrCAD_Capture\17.4.0\Capture.ini |

在 Capture.ini 配置文件当中检索

[Allegro Footprints],并将其修改为下面的形式,就可以通过

OrCAD 鼠标右键菜单当中的【Show

Footprint】,预览原理图符号所对应的 PCB 封装:

1 | [Allegro Footprints] |

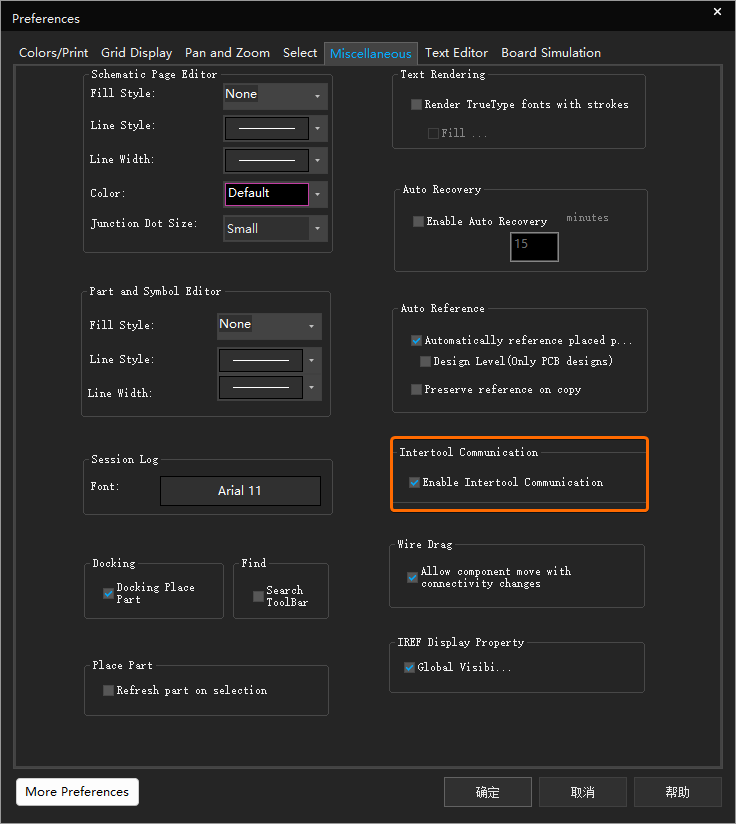

OrCAD 与 Allegro 交互式选择

首先,鼠标点击 OrCAD 顶部的

Options -> Preference;然后,切换【Preference】对话框至

Miscellaneous 选项卡;最后,勾选界面当中的如下选项:

1 | Intertool Commumicatiom -> Enable Intertool Commmication |

OrCAD 的选择过滤器

- 打开 OrCAD 在原理图上展开鼠标右键菜单,选中【Selection Filter】或者按下快捷键【Ctrl + I】打开选择过滤器对话框。

- 取消

Graphical Object项的勾选,就可以避免在框选原理图符号时,图形线框被错误的选中。

批量修改 OrCAD 原理图符号属性

- 首先,在 OrCAD 的原理图绘制界面按下快捷键【Ctrl +

I】,在打开的 Selection Filter 对话框中只勾选

Parts项。 - 然后,在 OrCAD

原理图绘制界面,使用鼠标框选需要批量修改属性的元件,点击鼠标右键菜单上面的

Edit Properties...选项,或者也可以直接按下快捷键【Ctrl + E】。 - 最后,在随后打开的 Property Editor

界面,鼠标选中整行或者整列的属性值,通过右键菜单中的

Edit或者Display,就可以对原理图符号的各项属性值(包括参数可见性、PCB 封装信息等)进行批量调整。

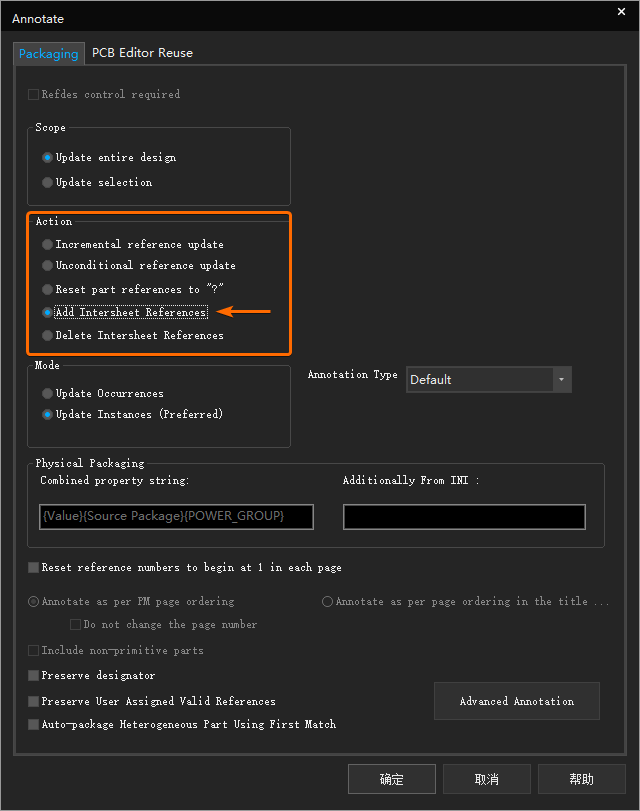

为原理图添加 Intersheet References

在分页原理图的跨页连接符前面加上引用的原理图页码,鼠标选中当前所要操作的

OrCAD

原理图工程,展开右键菜单选择【Annotate...】项,在弹出的

Annotate 原理图注释对话框,鼠标点击

Add Intersheet References,并进行下图所示的设置:

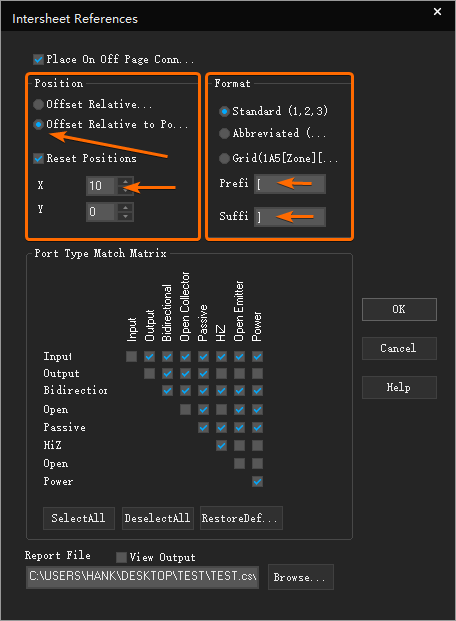

点击确定按钮之后,在弹出的【Intersheet References】对话框里执行如下的通用设置:

在上面【Intersheet References】对话框当中,各个设置项的具体意义如下所示:

Place On OffPage Connectors:是否在跨页连接符放置引用页码(通常选择该项);Position -> Offset Relative to Port:以跨页连接符作为偏移基准;Position -> Offset Relative to Port Name:以跨页连接符的名称作为偏移基准(通常选择该项);

Reset Positions -> X Offset:X 轴偏移量(不能为负值),通常设置为10;Reset Positions -> Y Offset:Y 轴偏移量(不能为负值),通常设置为0;

Format -> Standard[1,2,3]:页码格式为数字形式(通常选择该项);Format -> Abbreviated[1..3]:页码格式为缩写形式;Format -> Grid[1A5[Zone][Num]]:页码格式为行号 + 列号 + 页码的格式;

Format -> Prefix:原理图页码的前缀,可以设置为[]、{}、(),通常设置为[];Format -> Suffix:原理图页码的后缀,可以设置为[]、{}、(),通常设置为[];

网络别名、端口、跨页连接符的区别

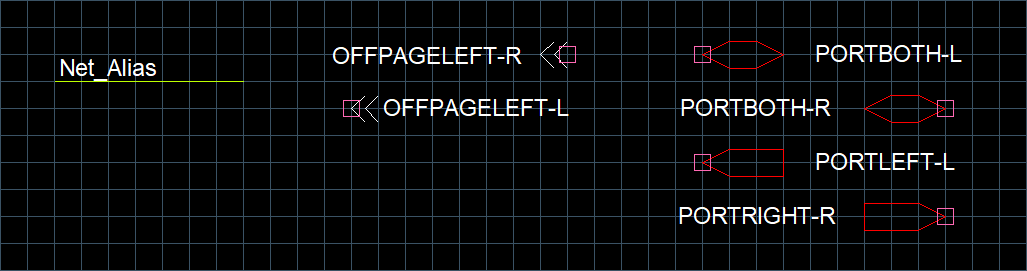

使用 OrCAD 绘制原理图的时候,经常使用到下图从左至右展示的 网络别名、端口、跨页连接符 三个符号,虽然它们都用于表示相同属性名称之间的连接关系,但是各自的作用范围并不相同:

- 网络别名【Net Alias】:无独立符号,需要放置到导线上面,作用范围仅仅局限于当前原理图;

- 端口【Port】:通常用于层次原理图设计,用于建立具有相同属性的端口之间的连接关系;

- 跨页连接符【Off-Page Connector】:作用于多张原理图之间,但是不能在一张原理图里多次放置;

OrCAD 批量指定字体和图形的颜色

- 首先,依次点击 OrCAD 菜单栏上的

View -> Toolbar -> Command Window; - 然后,使用鼠标框选当前需要指定颜色的 文字 和 图形;

- 最后,在【Command Window】窗口输入

SetColor 颜色代码;

1 | SetColor 0 // 设置为黄色 |

常见 ORCAP 原理图错误处理

ORCAP-1589 多个网络别名

ORCAP-1589

错误是指该网络存在多个网络别名,可能会造成短路。

1 | WARNING(ORCAP-1589): Net has two or more aliases - possible short ? |

在 OrCAD 当中,属性为 POWER

的引脚,引脚符号的名称,必须同时为对应网络的名称,否则就会报出该错误,该问题可以通过下面几种方式解决:

- 属性为

POWER的引脚符号名称,保持其与对应网络的名称相同。 - 将

POWER属性修改为Passive,就可以避免引脚名称与网络名称相同的问题。 - 取消【DRC】当中的

Physical Rules检查,即在【Design Rules Check】对话框【Rules Setup】界面当中,取消Check power ground short在Batch项下面的勾选。

ORCAP-1376 多个网络别名

Heterogeneous [ˌhetərəˈdʒiːniəs]

类型的元件由多个部分组成,如果 OrCAD

原理图当中,放置了多个 Heterogeneous

元件,那么在分配位号的时候,OrCAD 的 Session

Log 窗口就会报出 ORCAP-1376 错误信息:

1 | ERROR(ORCAP-1376): Cannot package part 'SFP?A(Value M42F-08P-020-P002G_0) at location (121.92, 139.70) on page 09-ETH-SFP-[0-6]', with multiple schematic symbols representing different functions. Ensure package has similar parts. |

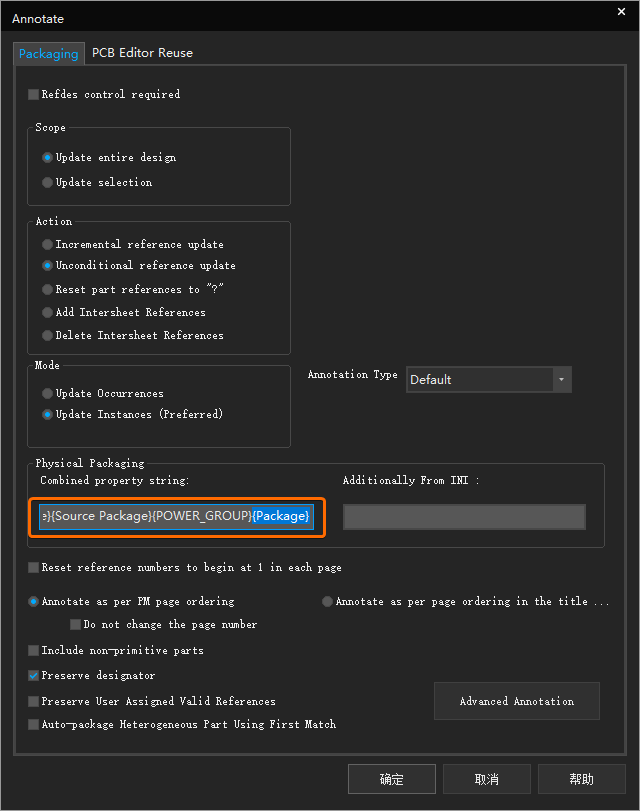

导致该错误的原因是 OrCAD 无法分辨哪几些部分属于同一个 Heterogeneous 元件,解决该问题可以遵循如下步骤:

- 为 Heterogeneous

元件的每一个组成部分,都添加一个自定义的

Package属性; - 确保每一个 Heterogeneous 元件的各个组成部分

Package属性都相同; - 分配位号的时候,在【Annotate】窗口的

Combined property string输入框内容的尾部添加{Package};

OrCAD/Allegro 交互式网表的导入导出

OrCAD 里设置交互功能

鼠标点击 OrCAD 菜单栏上的

Options -> Preferences...,切换至【Preferences】对话框的【Miscellaneous】选项卡,勾选该选项卡下的

Intertool Communication,开启 OrCAD

的工具交互功能:

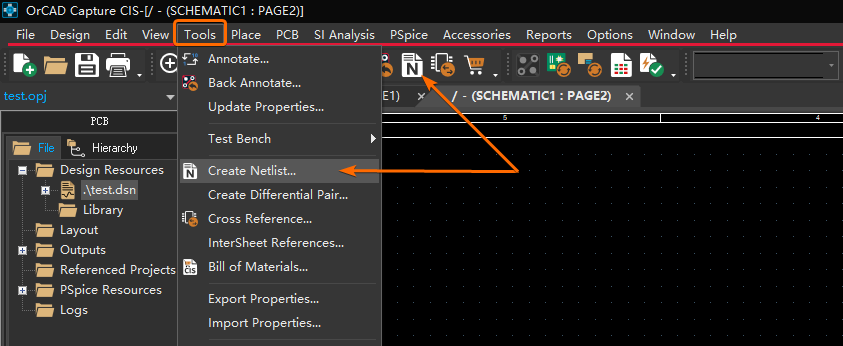

OrCAD 导出网表

鼠标点击 OrCAD 菜单栏上的

Tools -> Create Netlist...

或者直接点击工具栏上的图标,打开【Create Netlist】对话框:

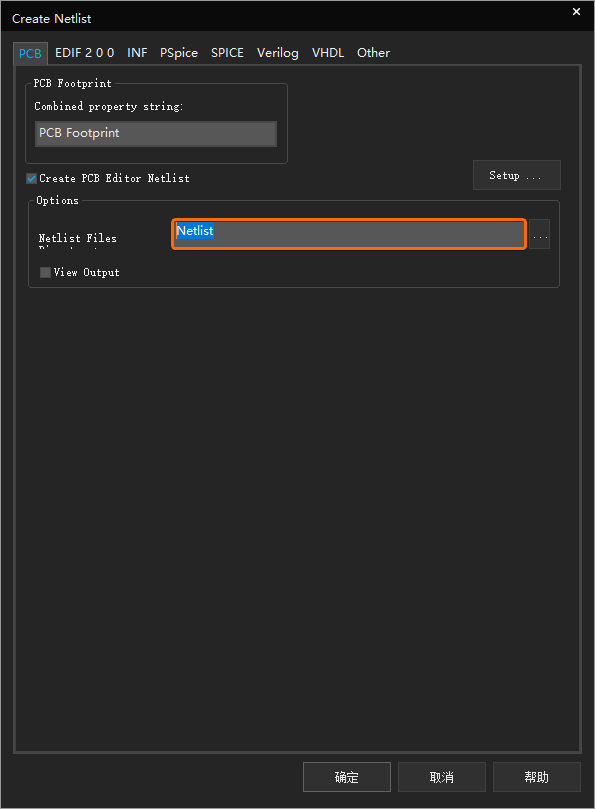

紧接着在【Create Netlist】对话框里指定 .dat

网表文件导出的路径:

OrCAD 导出的网表文件主要由

pstchip.dat、pstxprt.dat、pstxnet.dat

三个文件组成,它们各自的功能和用途请参考下面的表格:

| 网表文件名称 | 功能描述 |

|---|---|

pstchip.dat |

描述原理图当中元器件的引脚信息; |

pstxprt.dat |

描述原理图当中元器件的封装信息; |

pstxnet.dat |

描述原理图当中各个元器件之间的网络连接关系; |

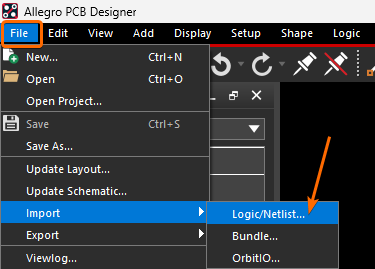

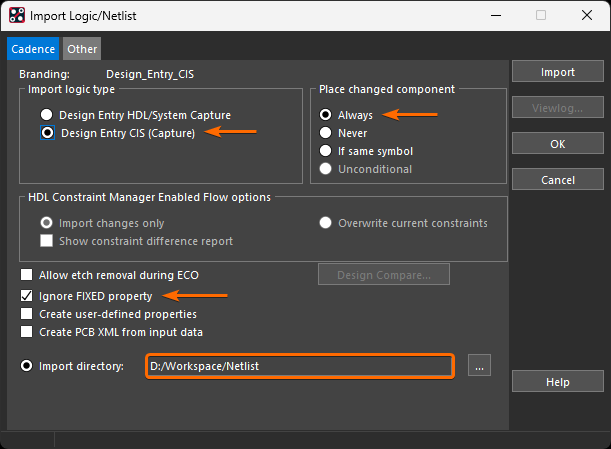

Allegro 导入网表

鼠标点击 Allegro 菜单栏上的

File -> Import -> Logic/Netlist...,打开【Logic/Netlist...】对话框:

接下来在打开的【Logic/Netlist...】对话框中进行如下的设置(注意指定 OrCAD 网表文件的所在目录):

【Allegro 自定义快捷键】

合理配置 Allegro 的快捷键,可以大大提升 PCB 设计效率。特别是对于从 Altium Designer 或者 PADS 迁移过来的工程师而言,可以最大化的保留自己的操作习惯:

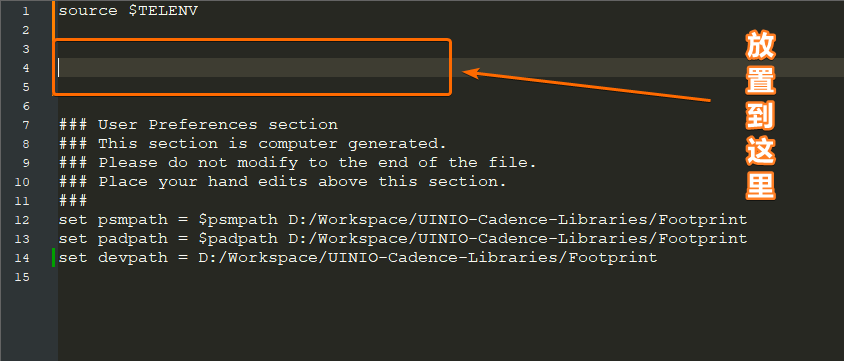

1 | source $TELENV |

在 Allegro 的【Command】窗口当中,输入如下的命令可以打印出当前所使用的用户环境变量路径:

1 | echo $localenv |

通过修改该环境变量路径下的 env 文件,就可以使用

alias 和 funckey

命令进行自定义快捷键。根据当前 Cadence

安装环境的不同,打印出的用户环境变量路径会存在如下两种情况(按需修改即可):

C:\Cadence\SPB_Data\pcbenvC:\Cadence\SPB_17.4\share\pcb\text

如果 env 文件位于

C:\Cadence\SPB_Data\pcbenv 目录下,自定义的配置信息需要放到

env 文件的如下位置,以避免被其它配置项覆盖:

注意:

C:\Cadence\SPB_Data\pcbenv目录下的env文件顶部必须保留source $TELENV字段,否则会导致 Allegro 启动错误。

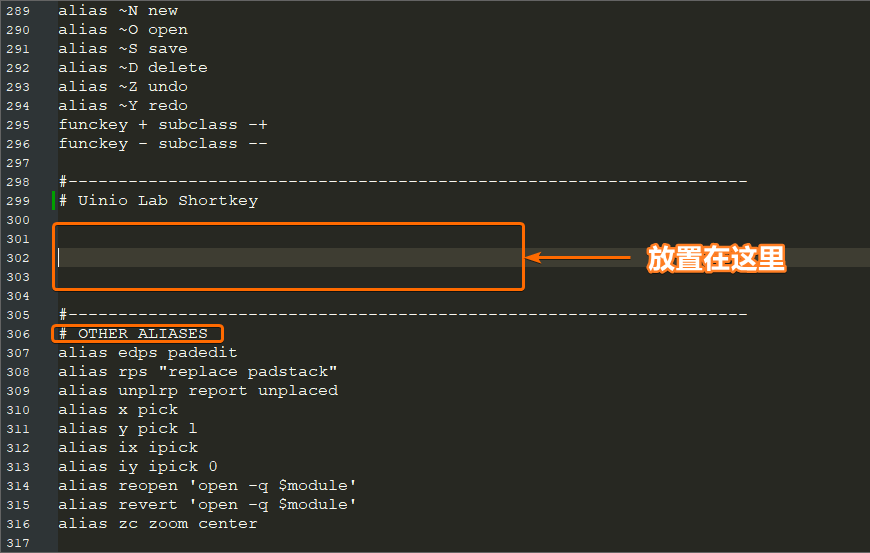

如果 env 文件位于

C:\Cadence\SPB_17.4\share\pcb\text\env

目录下,自定义配置信息则建议放置到 env 文件的如下位置:

alias 命令用于对 Allegro

命令取别名,使用时需要同时按下 特殊功能键 或者

特殊功能键 + 字母/数字

组合,并不能定义单独的字母快捷键:

1 | alias <alias> <command to run> |

alias F2 Add Connect:这里F2是指键盘上的特殊功能键【F2】;alias ~W Add Connect:符号~用于表示Ctrl按键,表示的是同时按下【Ctrl + W】;alias CF2 Add Connect:字母C等同于Ctrl按键,表示的是同时按下【Ctrl + F2】;

注意:

alias命令里的C代表按键【Ctrl】,S代表按键【Shift】。

funckey

命令用于定义单独的字母快捷键,在 PCB

版图上按下该字母,或者在Allegro

的【Command】窗口输入该命令,就可以执行相应的功能:

1 | funckey <user-defined key or name> <command to run> |

funckey r iangle 90:小写字母r用于宣传正在移动的 PCB 封装 90° 度;funckey R iangle 45:大写字母R用于宣传正在移动的 PCB 封装 45° 度;

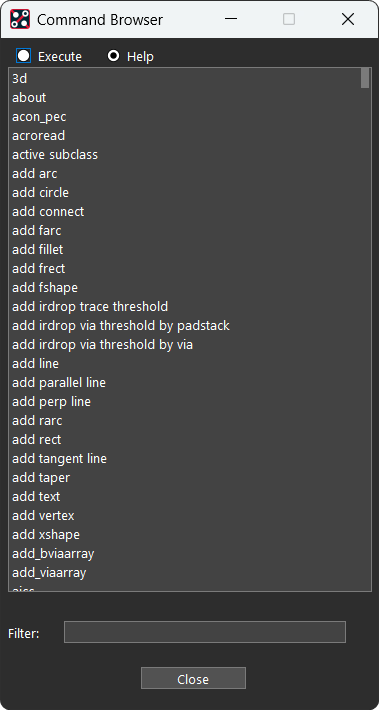

鼠标依次点击 Allegro 菜单栏上的【Tools -> Utilities -> Keyboard Commands】,就可以打开命令浏览器【Command Browser】窗口,浏览当前 Cadence 可以被执行和定义的命令:

注意:命令浏览器当中的【Execute】用于执行列表中的命令,【Help】用于单击查看列表当中命令的帮助文档。

关闭 Allegro 手动保存提示

- 首先,鼠标依次点击 Allegro 菜单栏上的

Setup -> User Preferences...; - 然后,在弹出界面【User Preferences Editor】左下角的

Search for preference输出框里输入save关键字,然后按下【Search】按钮或者回车键。 - 最后,勾选

noconfirm_savedb的【Value】和【Favorite】即可关闭 Allegro 的保存提示功能。

指定 Allegro 的 PCB 封装库路径

- 首先,鼠标依次点击 Allegro 菜单栏上的

Setup -> User Preferences...; - 然后,打开【User Preferences Editor】对话框左侧树形菜单中的

Paths -> Library;

勾选打开界面当中

devpath、padpath、psmpath

后的【Favorite】选项,并且指定其【Value】项对应的资源路径:

devpath指定第三方网表文件的保存路径(如果当时导入的是 OrCAD 生成的网表,则保持默认即可);padpath用于指定 PCB 封装焊盘的存放路径。psmpath用于指定 PCB 封装的存放路径。

预览 Allegro 里导入的 PCB 封装

- 当 Allegro 新建或者打开

.brd文件之后,鼠标点击 Allegro 菜单栏上的Place -> Manually; - 在弹出的【Placement】对话框中选择【Advanced

Settings】选项卡,然后勾选界面上的

Library选项; - 将选项卡切换回【Placement】对话框当中的【Placement List】选项卡;

- 切换至下拉列表里的【Package symbols】,就可以浏览到当前引用的 PCB 封装(可以通过右侧的【Selection filters】查询和过滤):

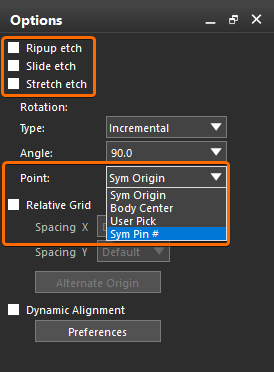

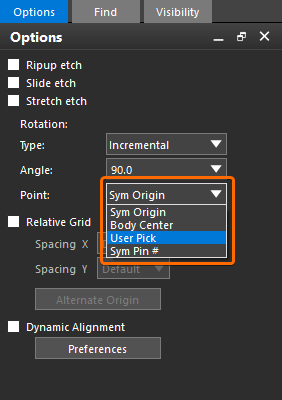

Allegro 的 Move 命令选项

在 Allegro 当中执行元素移动命令 Move 时,需要注意【Option】窗口中的如下参数选项:

Ripup etch:移动对象时,去除所有的走线与过孔;Slide etch:移动对象时,保留走线和过孔,但走线伴随对象平滑移动;Stretch etch:移动对象时,保留走线和过孔,但走线伴随对象任意角度移动;上述三项都不勾选:表示只移动对象,完全不影响走线和过孔;

Point 属性用于设置元素旋转时的基准点,Allegro 提供了如下几种方式:

Sym Origin:以元件封装的原点作为基准点;Body Center:以元件的place_bound几何中心作为基准,常用于各个元件的就地旋转;User Pick:以用户鼠标单击的选择点作为基准,常用于多个元件的整体旋转;Sym Pin#:以指定的元件引脚编号作为基准点,常用于元件结构相关的定位;

注意:上述参数中的

Sym Origin和Body Center与 PCB 封装绘制得是否规范密切相关。

Allegro 的 ROOM 模块化布局

- 添加

ROOM属性:OrCAD 当中为元件添加自定义的ROOM属性(相同的模块,属性值相同)。 - 绘制

ROOM框:鼠标依次点击 Allegro 菜单栏的Setup -> Outlines -> ROOM Outline,打开【ROOM Outline】对话框之后,直接在 Allegro 的绘制区域点击拖动,就可以为具有相同ROOM属性值的元件绘制出一个放置区域。 - 根据

ROOM属性放置元件:鼠标依次点击 Allegro 菜单栏的【Place -> Quickplace】,勾选对话框里【Placement filter】下的Place by room,并且在后面的下拉列表当中,指定当前需要放置的ROOM属性元件,最后点击对话框上的【Place】按钮,即可将具有相同ROOM属性值的元件摆放到指定的Outline区域当中。

开启 Allegro 的移动对齐辅助线

- 在 Allegro 当中,选择移动命令,然后按下鼠标右键;

- 依次选择弹出菜单中的

Options -> Dynamic Aligment -> Enable,就可以开启移动对齐辅助线;

从 Allegro 工程导出 PCB 封装

从 Allegro 导出 .dra 封装库源文件

使用 Allegro 打开已有的 PCB 版图文件 .brd

之后,可以导出当前 PCB 版图所涉及的各种封装文件:

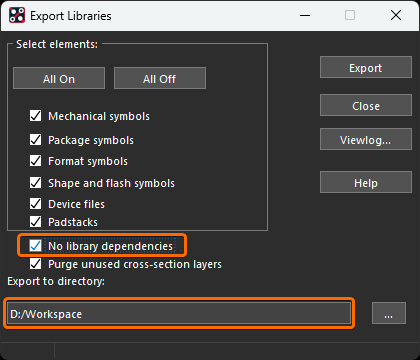

- 鼠标依次点击 Allegro 菜单栏上的

File -> Export -> Libraries...; - 在弹出的【Export Libraries】对话框当中,勾选

No library dependencies,并在Export to directory填写 PCB 封装的导出路径; - Allegro 就会自动将 PCB 封装源文件

.dra、PCB 封装文件.psm、PCB 封装描述文件.txt导出到指定的目录当中。

从封装库源文件导出 .pad 焊盘文件

基于已有的 PCB 封装源文件 .dra,可以进一步导出指定的

.pad 焊盘文件:

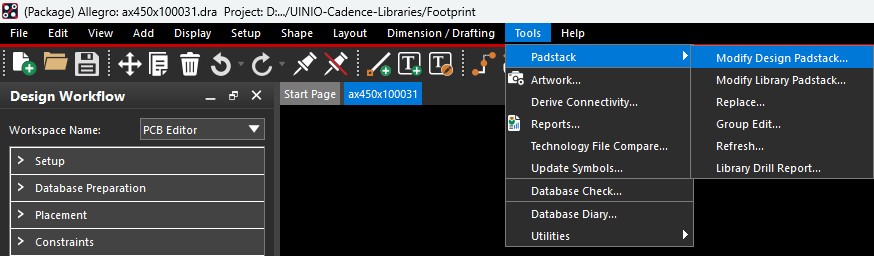

- 依次点击 Allegro 菜单栏上的

Tools -> Padstack -> Modify Design Padstack... - 在 Allegro 当中打开

.dra文件,并且选中一个焊盘; - 然后展开鼠标右键,选择【Edit】对该焊盘进行编辑,此时会弹出【Padstack Editor】窗口;

- 鼠标依次选择弹出界面当中的【File -> Save As...】,就可以将

.pad焊盘文件导出到指定目录;

从封装库源文件导出 .txt 封装信息

基于已有的 PCB 封装源文件 .dra,还可以导出以

.txt 作为后缀的 PCB 封装信息文件:

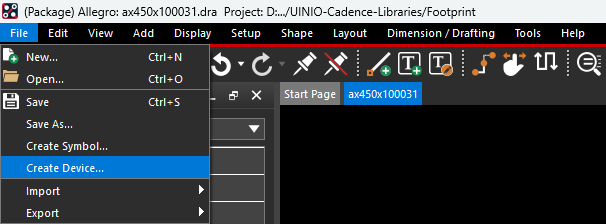

- 鼠标依次点击 Allegro 菜单栏上的

File -> Create Device...; - 在弹出的【Create Device

File】窗口选择当前所要导出的元件类型

Device Type(默认包含IC、IO、DISCRETE三个选项); - 按下【OK】按钮之后,就会自动将

.txt封装信息文件导出至当前.dra文件所在的目录;

从封装库源文件导出 .psm 封装文件

基于已有的 PCB 封装源文件 .dra,可以进一步导出

Allegro 实际使用的 PCB 封装文件 .psm:

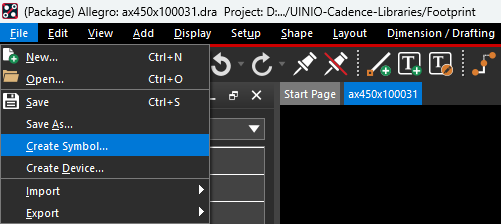

- 鼠标依次点击 Allegro 菜单栏上的

File -> Create Symbol...; - 在弹出的【Create Symbol】对话框当中,选择

.psm封装文件的保存位置; - Allegro 就会自动将

.psm封装文件导出到指定的目录;

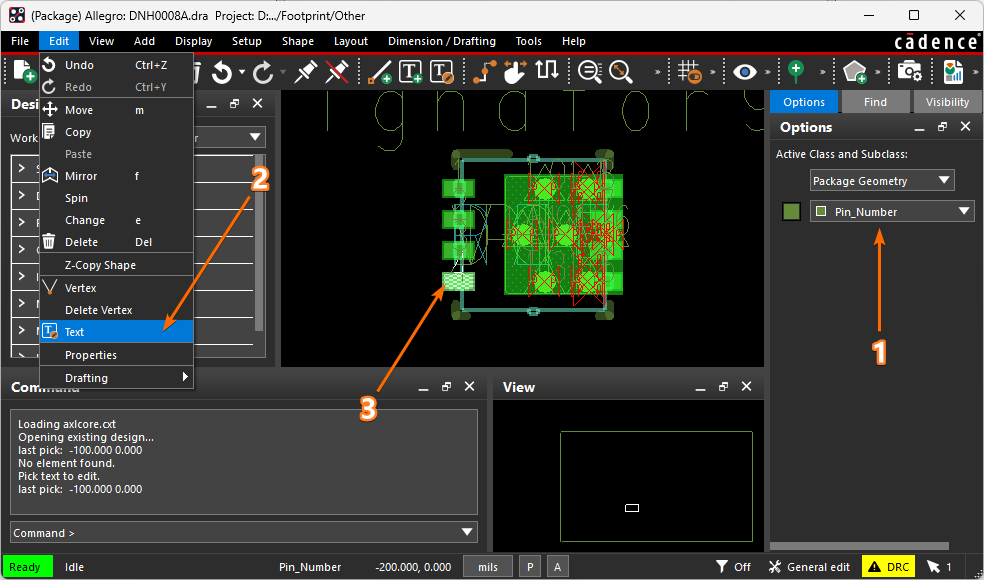

修改 .dra 封装源文件的 Pin Number

- 使用 Allegro 打开

.dra封装源文件; - 切换 Allegro 界面右侧【Options】选项卡里的

Active Class 为

Package Geometry,Subclass 为Pin_Number; - 鼠标点击 Allegro 菜单栏上的

Edit -> Text; - 鼠标选中 Allegro 工作区的封装焊盘,即可以实现对

Pin Number的修改。

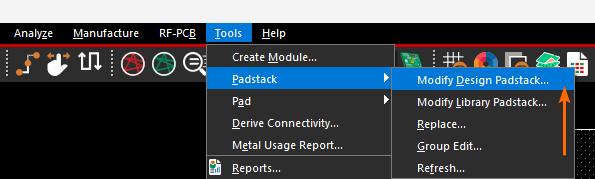

Allegro 导出 .dra 中的 .pad 焊盘文件

使用 Allegro 打开需要处理的 .dra

封装源文件,鼠标点击【Tools -> Padstack -> Modify Design

Padstack】

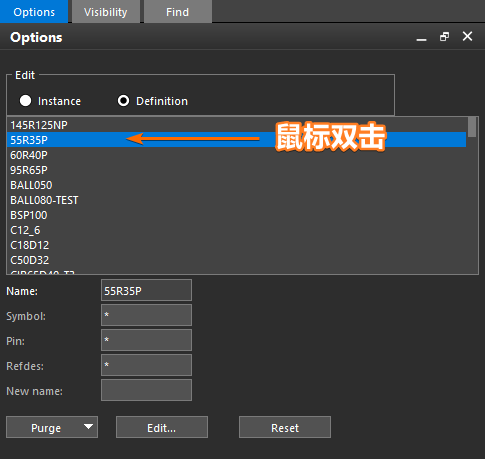

鼠标双击 Allegro 右侧工作面板【Option】选项卡上面,当前需要导出的焊盘名称:

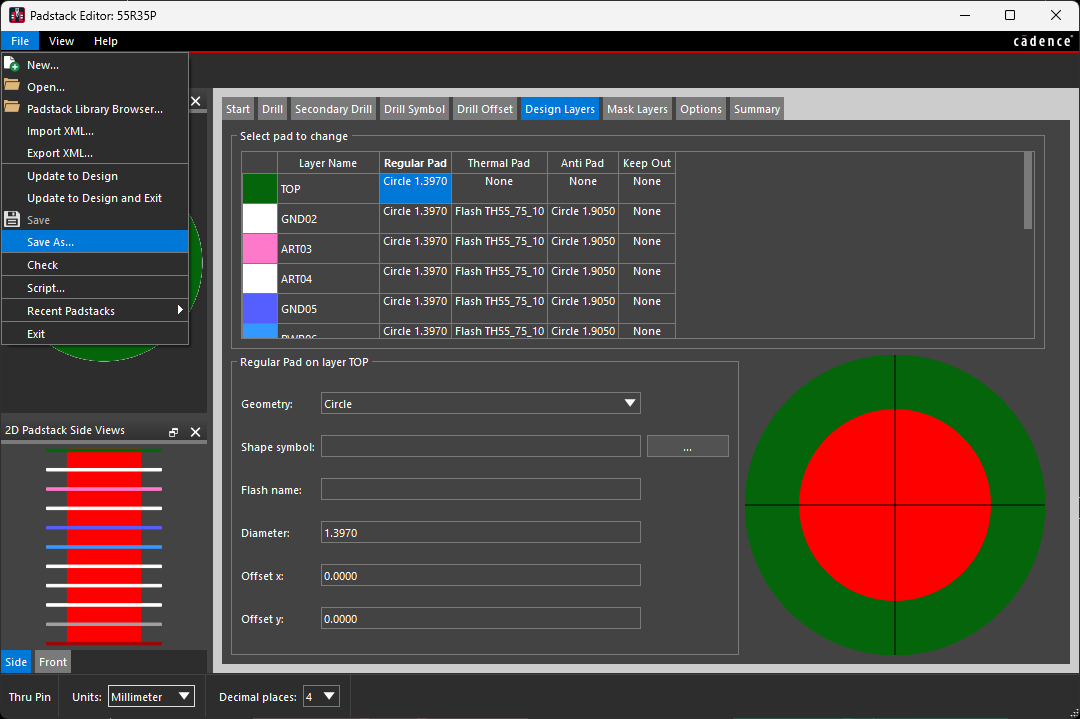

在弹出的【Padstack Designer】窗口,鼠标依次点击

File -> Save As...,即可将 .pad

焊盘文件保存到其所属 .dra 封装源文件所在的目录:

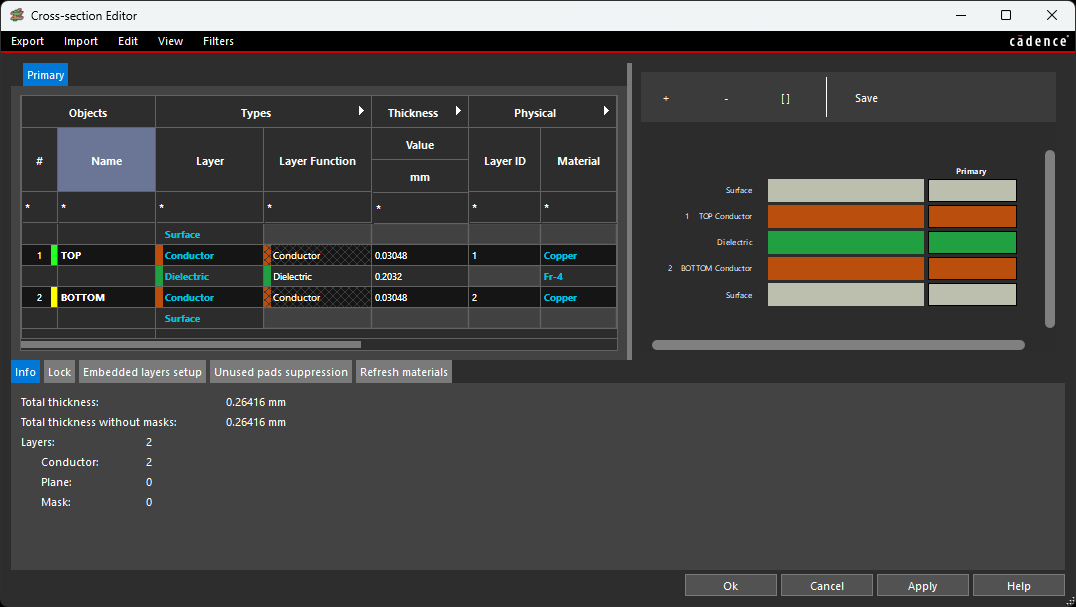

Cross Section 叠层的定义与添加

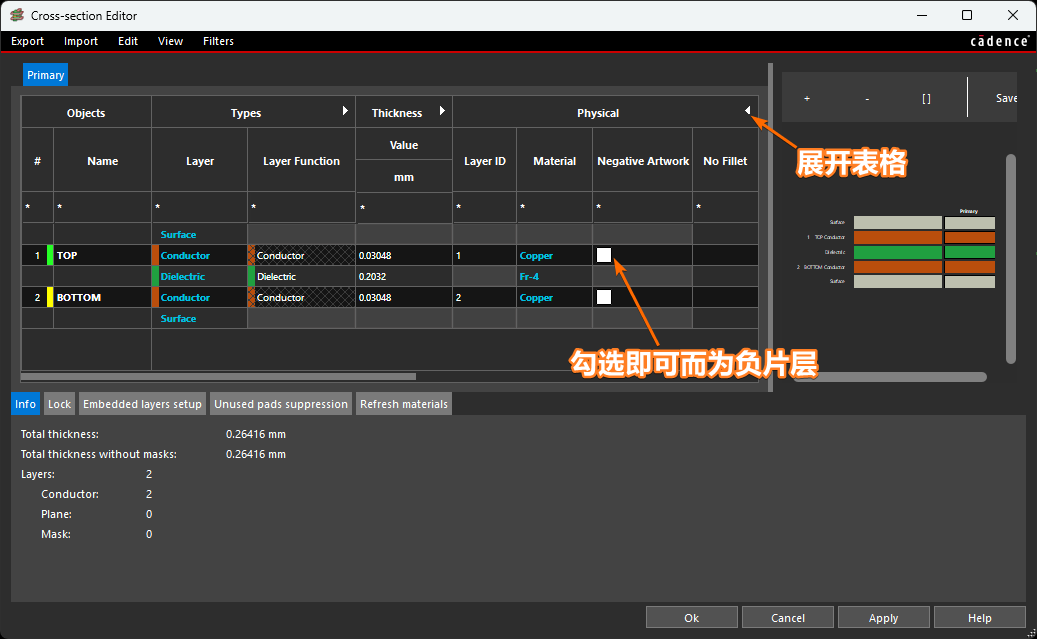

官方建议在 Allegro 当中,信号层采用正片层方式处理,电源层和接地线层采用负片层方式处理,这样可以减少工程文件的数据量,并且提升 EDA 软件的运行效率:

- Conductor:正片层,即用于正常走线的信号层;

- Plane:负片层,被默认铺铜填充(走线被视为分割线)的电源层或者接地层,也被称为内电层;

注意:内电层在 Allegro 的

Anti Etch层,使用大于或者等于15mil的分隔线进行分割。然后使用鼠标右键菜单的Assign Net分配网络。

鼠标点击 Allegro 菜单栏上的

Setup -> Cross Section

项,或者直接点击菜单栏上的【Xsection】按钮,就可以进入 PCB

叠层管理器【Cross-section Editor】进行相关参数的设置:

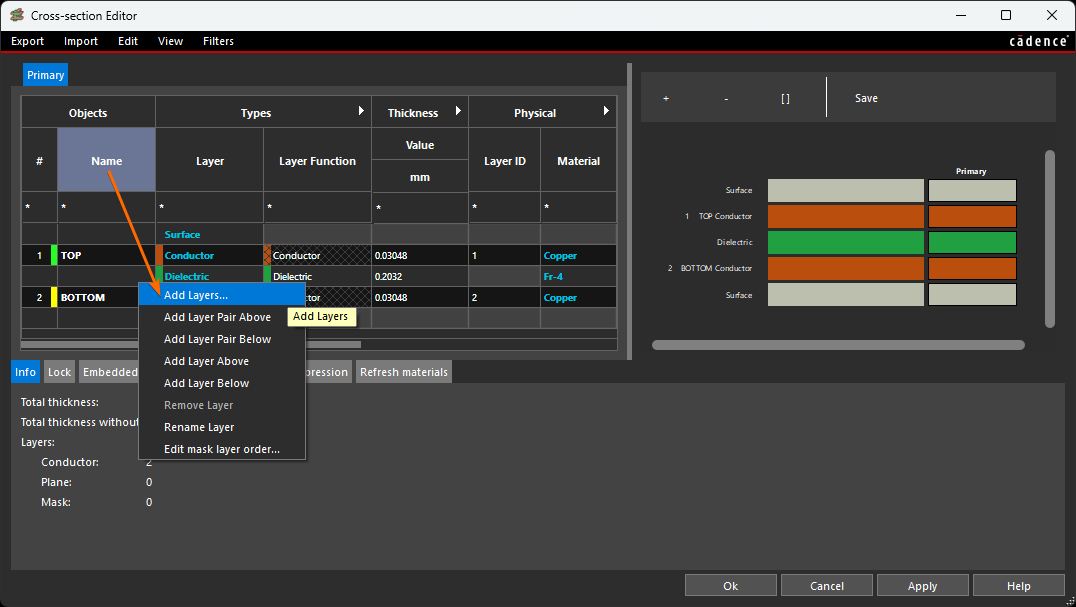

鼠标点击【Cross-section Editor】窗口当中表格的 Name

列,选择右键菜单上的【Add Layer】项,就可以添加新的 PCB 叠层:

注意:Dielectric [ˌdaɪɪˈlektrɪk] n.电介质,绝缘体。

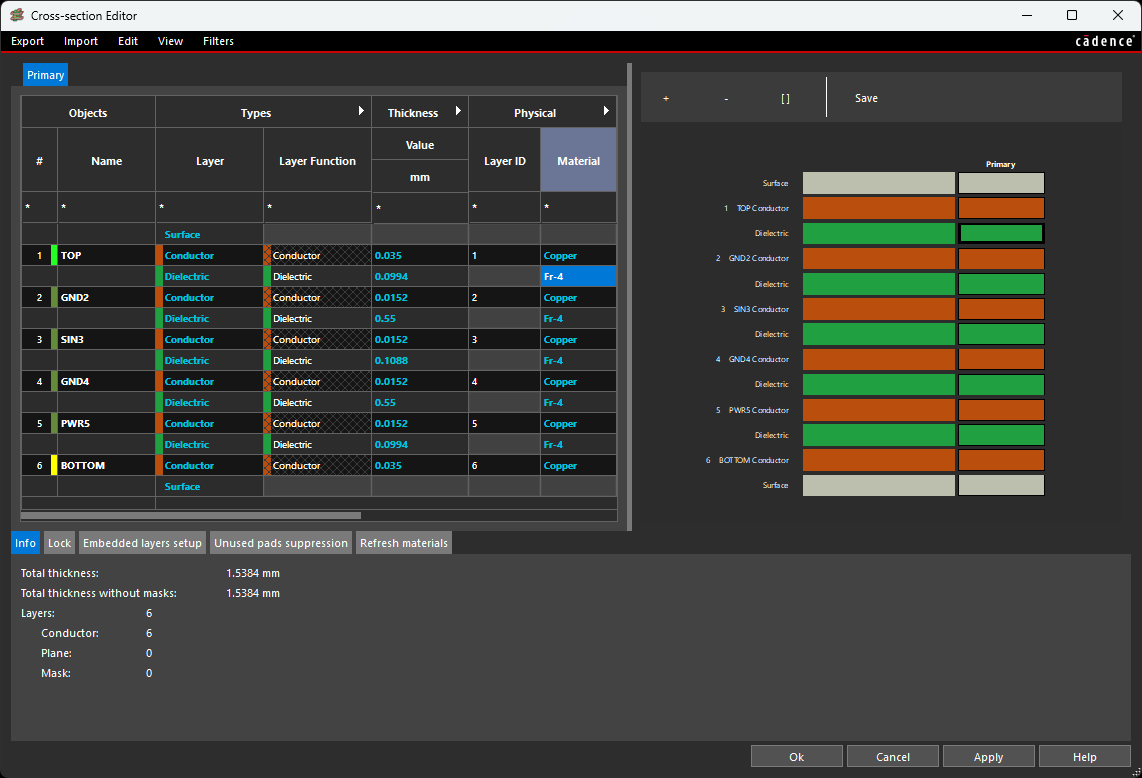

鼠标双击 Name 列还可以修改叠层的名称,命名方式推荐使用

层名称缩写 + 层顺序编号

格式,例如:TOP、GND2、SIN3、SIN4、PWR5、BOTTOM

等:

注意:除此之外还可以根据 PCB 生产企业提供的工艺制造参数(例如《嘉立创层压结构》),选择相应的 PCB 叠层

厚度(Thickness)、材质(Material)、电导率(Conductivity)、介电常数(Dielectric Constant)等参数。

值得注意的是,PCB 的负片层也是在【Cross-section Editor】窗口当中进行设置的:

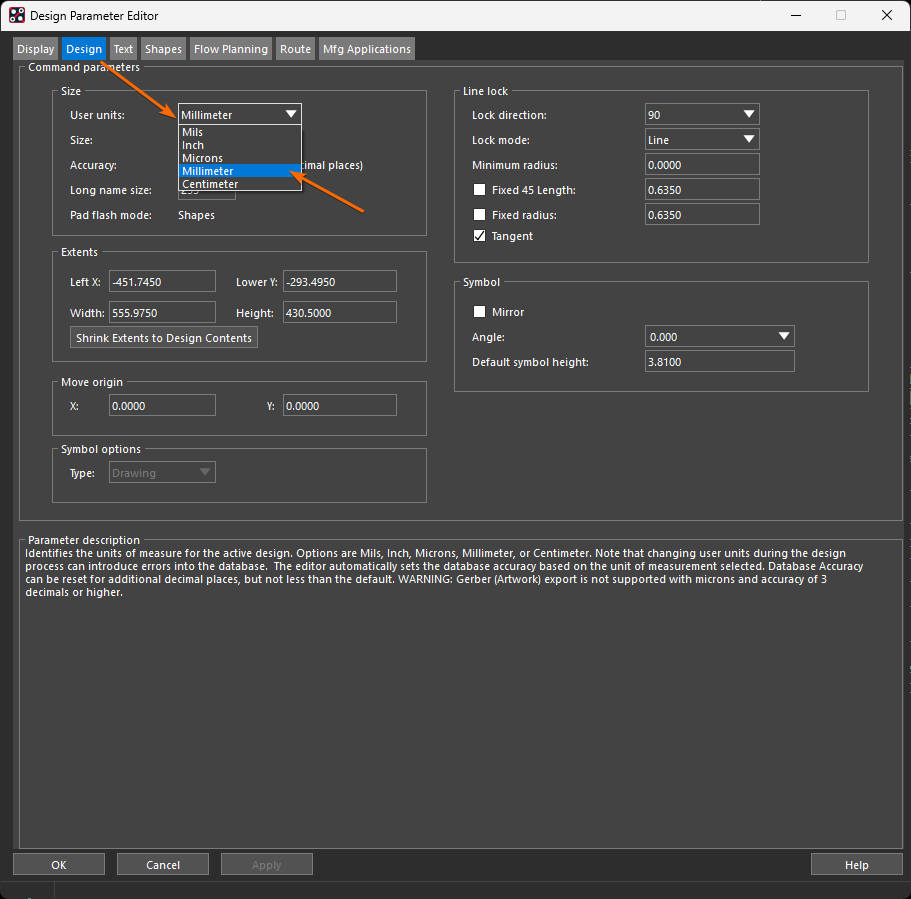

切换 Allegro 单位为 mil 或者 mm

鼠标依次选择 Allegro 菜单栏上的

Setup -> Design Parameters...,在弹出的设计参数编辑器【Design

Parameters Editor】窗口,修改【Design】选项卡下面的

User units 下拉菜单:

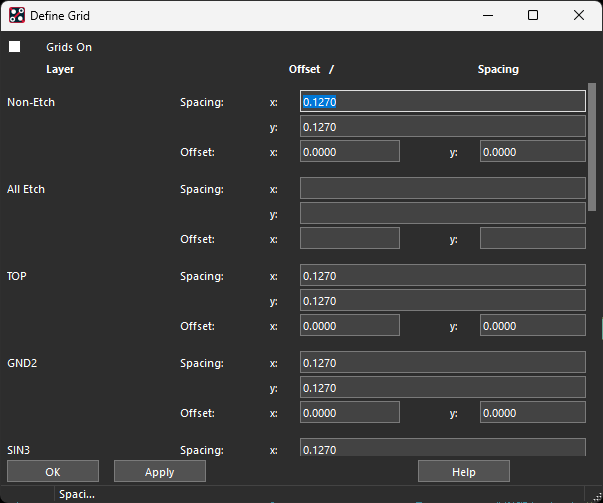

设置 Allegro 工作区栅格大小

鼠标依次选择 Allegro 菜单栏上的

Setup -> Grids...,在弹出的栅格定义窗口【Define

Grid】,就可以分别设置各个叠层的栅格大小(设置为

5mil 0.127mm 更加方便元器件对齐):

注意:为了方便元件对齐与摆放,推荐布局时使用

5mil/0.127mm的栅格。

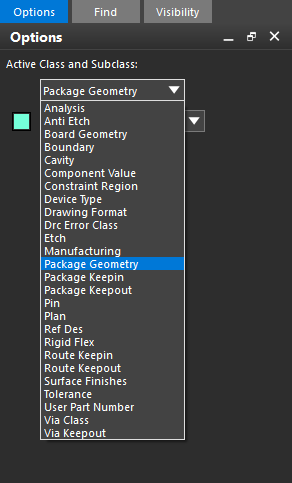

Allegro 的 Class 与 Subclass 概念

Allegro 当中的类型

Class 与 子类型 Subclass

是这款设计工具当中的基本概念,当前绘制在 PCB 版图当中的所有对象都会以

Class 和 Subclass

进行管理。就像每一名学生都归属为某个年级与某个班级,这里年级与班级就可以分别被理解为

Class 与 Subclass,下图展示了

Allegro 当中一些默认的 Class:

注意:在一些特定的系统

Class下面,可以创建自定义的Subclass。

例如电气层 Etch 这个

Class 下面,对应着 Top 和

Bottom 两个 SubClass:

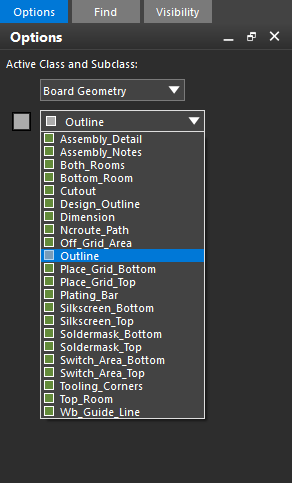

例如 PCB

版图相关的几何形状层(板框、丝印、尺寸标注等)都被放置在

Board Geometry 这个 Class

下面,对应着下图当中的各个 SubClass:

Allegro 当中 Class 和

Subclass 的名称本身没有任何意义,关键在于当把 PCB

版图上的对象放置到 Class 或者 Subclass

的时候,Allegro 如何去使用和处理这些对象。例如

Allegro 导入 PCB 封装的时候,PCB

封装当中的各个对象就会自动被放置在相应的 Class

当中进行管理,因为这些对象在 PCB 封装创建的时候就已经被指定了相应的

Class。

注意:Allegro 导入

.dxf板框时,默认会自动新建一个 PCB 文件覆盖当前的 PCB 工程,如果想将.dxf板框导入到当前的 PCB 文件,则必须勾选【DXF In】对话框当中的Incremental addition。

电气布局走线相关的常用 Class 与 Subclass 如下面表格所示:

| Class SubClass | top |

inner |

bottom |

all |

功能描述 |

|---|---|---|---|---|---|

anti etch |

✔ | ✔ | ✔ | ✔ | 用于切割覆铜 |

etch |

✔ | ✔ | ✔ | - | 用于电气连接 |

package keepin |

- | - | - | ✔ | 允许放置元件区域 |

package keepout |

✔ | - | ✔ | ✔ | 禁止放置元件区域 |

route keepin |

- | - | - | ✔ | 允许布线区 |

route keepout |

✔ | ✔ | ✔ | ✔ | 禁止布线区 |

via keepout |

✔ | ✔ | ✔ | ✔ | 禁止过孔区 |

工艺装配标注 相关的常用 Class 与 Subclass 如下面表格所示:

| Class SubClass | board geometry |

package geometry |

ref des |

功能描述 |

|---|---|---|---|---|

soldermask_top |

✔ | ✔ | - | 顶层阻焊层 |

soldermask bottom |

✔ | ✔ | - | 底层阻焊层 |

silkscreen top |

✔ | ✔ | ✔ | 顶层丝印层 |

silkscreen_bottom |

✔ | ✔ | ✔ | 底层丝印层 |

pastemask top |

- | ✔ | - | 顶层助焊(钢网)层 |

pastemask_bottom |

- | ✔ | - | 底层助焊(钢网)层 |

place_bound_top |

- | ✔ | - | 顶层元件封装边界 |

place_bound_bottom |

- | ✔ | - | 底层元件封装边界 |

outline |

✔ | - | - | PCB 板框 |

assembly_top |

- | ✔ | ✔ | 顶层装配层 |

assembly_bottom |

- | ✔ | ✔ | 底层装配层 |

注意:

board geometry是指 PCB 板级的几何形状,package geometry是指 PCB 封装级的几何形状。

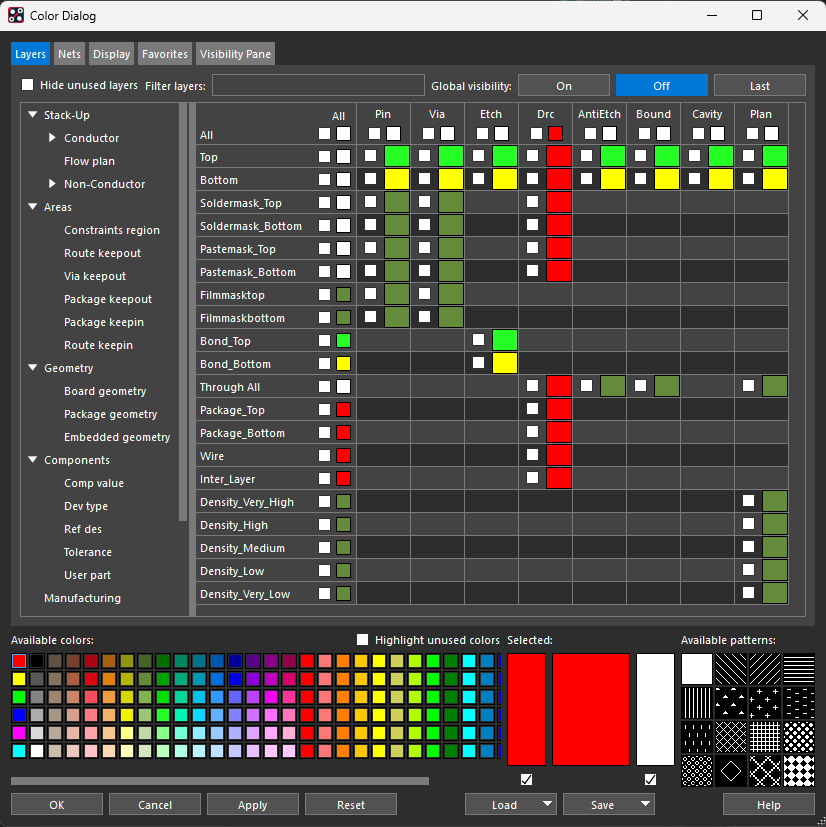

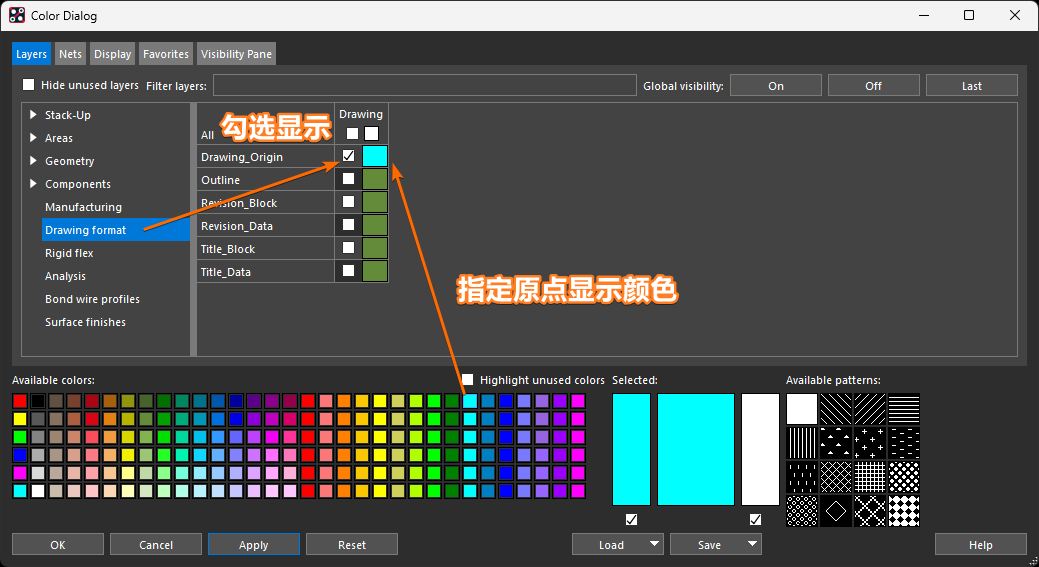

Allegro 颜色编辑器

鼠标点击 Allegro 菜单栏上的

Display -> Color/Visbility...

或者直接按下快捷键【Ctrl + F5】,就可以打开【Color

Dialog】对话框,使用 Allegro 进行 PCB

版图布局布线的时候,只需要开启如下的 Class 与

Subclass 的显示即可:

- 元件封装丝印:将

Geometry -> Package Geometry -> Silkscreen_Top/Silkscreen_Bottom显示为白色; - 元件封装位号:将丝印层

Component -> Ref des -> Silkscreen_Top/Silkscreen_Bottom显示为白色,将装配层Component -> Ref des -> Assembly_Top/Assembly_Bottom显示为蓝色; - 元件焊盘阻焊:将

Stack-Up -> Pin -> Soldermask_Top/Soldermask_Bottom显示为紫色; - PCB 板框:将

Geometry -> Border Geometry -> Outline/Design_Outline显示为亮黄色; - PCB 板级丝印:打开

Geometry -> Board Geometry下的丝印层Silkscreen_Top/Silkscreen_Bottom以及阻焊层Soldermask_Top/Soldermask_Bottom的显示;

导入 PCB 板框 & 允许布线区域

导入的板框放置在 Board geometry 这个

Class 的 Design Outline(兼容 17.x

之后的版本)和 Outline(虽然兼容 16.x

之前的版本,但是会导致 17.4 无法正常渲染 3D 模型)两个

SubClass 下面。放置板框的时候,在

Allegro 底部的【Command】输入框里键入

x 0 0,就可以让板框的左上角位置成为坐标原点。

- PCB 镂空区域:将需要板框图层 Z-Copy 到

Board geometry -> Design Outline(生成 3D 预览可见的板框); - PCB 镂空区域:将需要挖空处理的图层 Z-Copy 到

Board geometry -> Cutout(镂空板框当中的开孔区域); - PCB 允许布线区域:将允许布线的图层 Z-Copy 到

Route Keepin -> All(防止布线到板框区域之外),再鼠标点击右侧【Option】选项卡下的Contract,然后将图层的缩进Offset设置为10mil/0.254mm(防止铺铜之后,板框边沿的铜层割手); - PCB 禁止布线区域:将需要镂空的图层 Z-Copy 到

Route Keepout -> All(防止铺铜之后,铜层覆盖镂空区域),再鼠标点击右侧【Option】选项卡下的Expand,然后将图层的外扩Offset设置为10mil/0.254mm(防止铺铜之后,镂空的边沿即是板框边沿);

注意:如果系统提示板框超出绘制区域

SPMHA2-54: Cannot place outside of the drawing extends,则需要进入下面介绍的设计参数编辑器【Design Parameters Editor】,通过修改【Extends】选项卡下的相关参数,来调整绘制区域的大小。

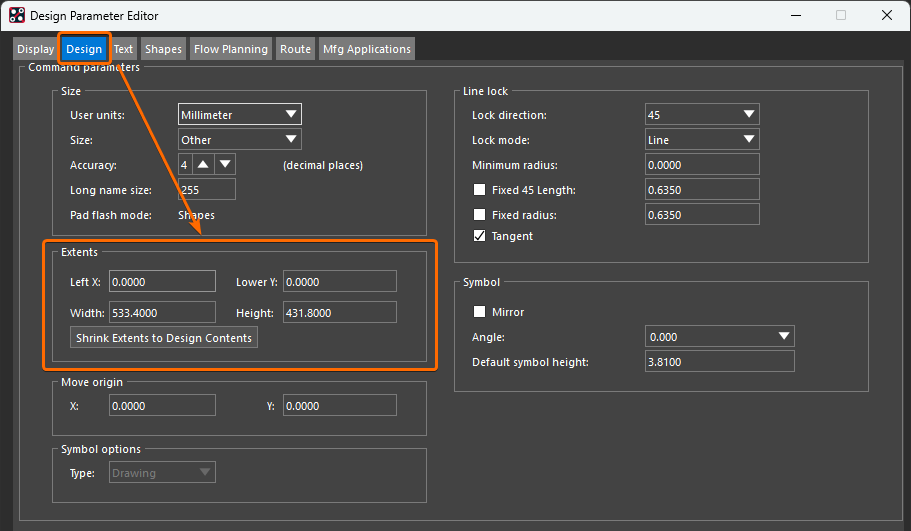

修改 Allegro 绘制区域尺寸

鼠标点击 Allegro 顶部菜单栏上的

Setup -> Design Parameters...,切换到【Design Parameters

Editor】对话框下的【Design】选项卡,通过调整 Extends

下的各项参数,就可以修改绘制区域的大小尺寸:调整绘制区域的尺寸。

LeftX和LeftY:表示绘制区域左下角起始的横坐标与纵坐标的值;Width和Heigth:表示绘制区域的宽度与高度;Move orign: 通过修改其X和Y取值,就可以调整当前绘制区域中原点的位置;

进行 3D Canvas 预览时的操作

按下 鼠标中键 并且拖动,就可以移动预览 PCB,按下 Shirt + 鼠标中键 则可以用于旋转 PCB 版图的 3D 预览效果。

注意:3D 预览当中的丝印颜色显示,需要在颜色管理器指定

Board Geometry/Silkscreen_Top和Board Geometry/Silkscreen_Bottom的颜色与可见性。

焊盘进入约束 Enhanced PadEntry

Allegro 走线的时候,展开鼠标右键菜单取消【Enhanced PadEntry】项的选择,可以避免走线必须从焊盘居中的位置进入焊盘中心。

元素按坐标精确移动

首先,在 Allegro 当中执行 move

命令,在右侧的【options】选项卡当中选择 User Pick:

Sym Origin:封装原点作为基准点(默认项);Body Center:以封装的Place Bound几何中心作为基准,通常用于单个元件的原地旋转;User Pick:以用户鼠标单击的点作为基准,通常用于多个元件的整体旋转;Sym Pin:以元件的引脚编号作为基准,通常用于元件结构定位;

然后,在 Allegro 底部的【Command】窗口输入执行下面的命令,就可以让指定的元素按照坐标进行移动:

- 绝对定位

x a b:基于右侧【0ption】选项卡当中选择的参考点,将元素移动到坐标a和b; - 相对定位

ix a:将元素沿着x轴的方向移动a个单位,相对移动命令不需要在【Option】选择参考点; - 相对定位

iy a:将元素沿着y轴的方向移动a个单位,如果当前单位为mm,那么输入iy -2就可以将元素向下移动2mm; - 相对定位

ix a iy b:将元素沿着x轴的方向移动a个单位,沿着y轴的方向移动b个单位;

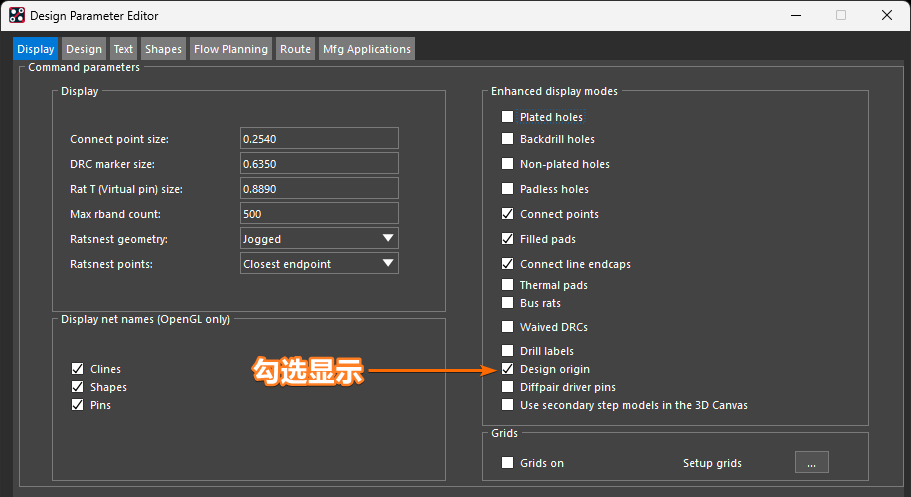

设置 PCB 版图原点的可见性和颜色

倒圆角与斜角

- 首先,需要将

Shape转换为Line,鼠标点击 Allegro 顶部菜单栏上的Shape -> Decompose Shape,然后框选目标元素执行操作; - 然后,再选择 Allegro菜单栏上的

Manufacture -> Drafting,进行Fillet(倒圆角)或者Chamfer(倒斜角),此时可以在右侧【Options】窗口填写倒角的半径、长度以及角度; - 最后,选择相邻的两条

Line,即可执行倒角操作;

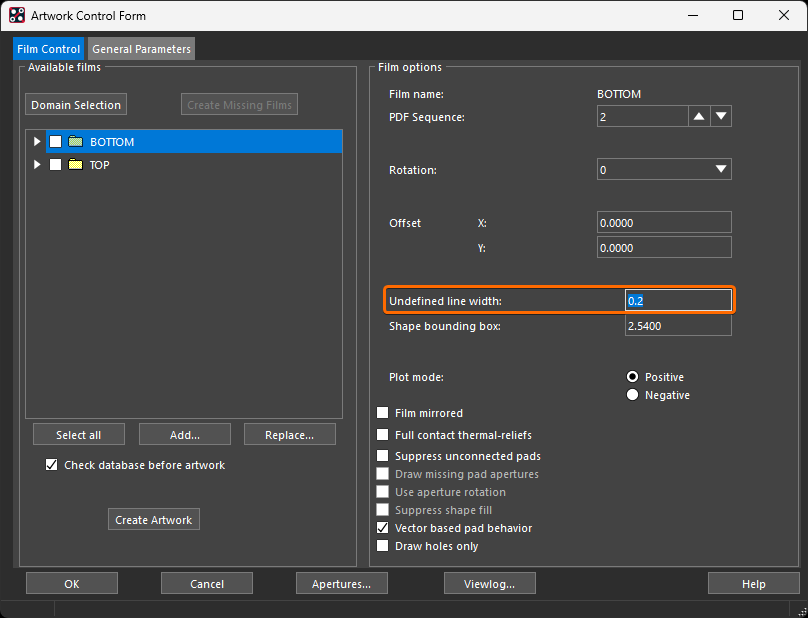

解决嘉立创板框/外形层缺失问题

导出 Gerber 光绘文件给嘉立创进行

PCB 打样的时候,为了避免出现 板框/外形层

缺失的问题,需要鼠标点击 Allegro 顶部菜单栏上的

Manufacture -> Artwork,将弹出窗口中的

Undefined Line Width 项修改为 0.2:

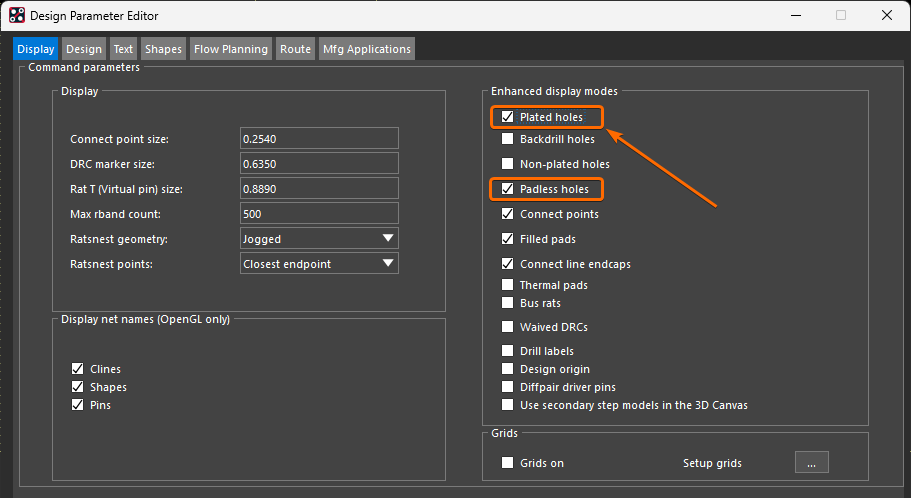

在 Allegro 当中显示过孔形状

鼠标点击 Allegro 菜单栏上的

Setup -> Design Parameter Editor,勾选【Display】选项卡下的

Plated holes 复选框(同时会自动勾选

Padless holes):

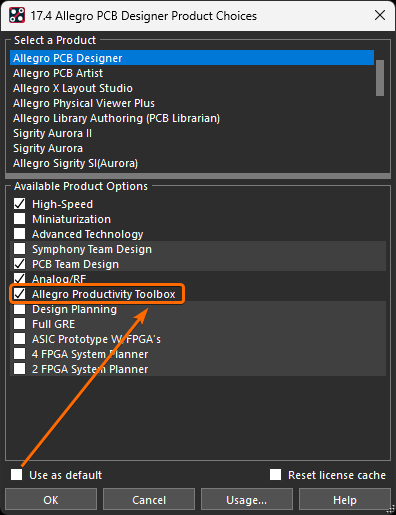

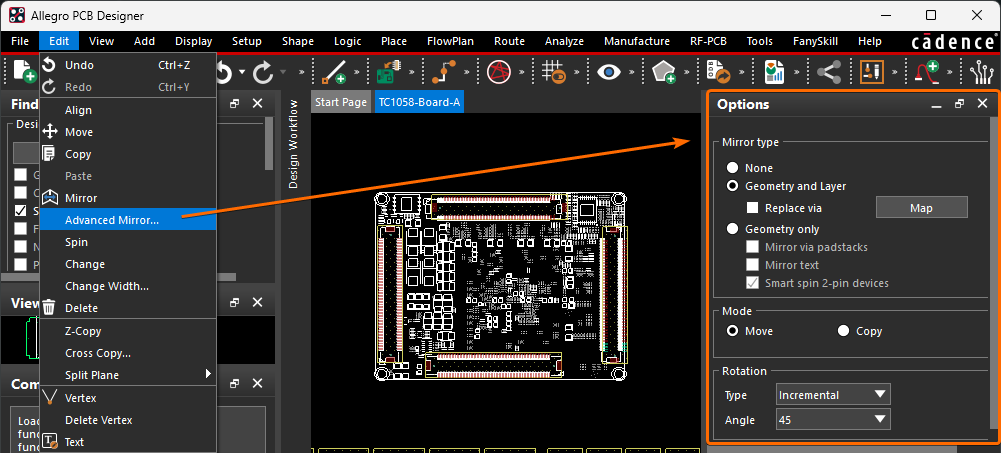

使用 Advanced Mirror 高级镜像

首先,鼠标点击 Allegro 顶部菜单栏上的

File -> Change Editor...,勾选

Allegro Productivity Toolbox 项:

然后,重新启动 Allegro 之后,再点击顶部菜单栏上的

Edit -> Advanced Mirror...,此时可以在右侧的【Option】窗口看到相关的设置项:

最后,鼠标框选当前工作区需要进行高级镜像处理的元素,并移动到空白处单击鼠标,即可执行相应的镜像操作。

镜像已经添加了的丝印文字

如果丝印文字在 PCB 顶层或者底层的显示出现镜像,那么可以通过如下所述的方式进行调整:

- 首先,勾选【Allegro PCB Designer Product Choices】当中的 Allegro Productivity Toolbox 选项,并且重新启动 Allegro;

- 然后,鼠标选择 Allegro 菜单上的

Edit -> Advanced Mirror...; - 接着,勾选 Find 窗口当中的

Text选项; - 接下来,勾选 Options 窗口当中的

Mirror type -> Geometry only -> Mirror text选项; - 最后,鼠标选择需要镜像的丝印文字即可;

丝印字符推荐参数

Allegro 丝印字符的

Width、Height、Line Space

三个参数,推荐采用下面的 换算公式 进行计算:

\[ \begin{cases} Width \\ Height = Width + 5/10 \\ LineSpace = Height + 10 \end{cases} \]

Photo Width 和 Char Space 按照如下

表格 的顺序加 1 递增即可:

| 编号 Text Blk | 宽度 Width | 高度 Height | 行间距 Line Space | 线宽 Photo Width | 字间距 Char Space |

|---|---|---|---|---|---|

| 1 | 20 mil |

25 mil |

35 mil |

4 mil |

4 mil |

| 2 | 30 mil |

35 mil |

45 mil |

5 mil |

5 mil |

| 3 | 35 mil |

45 mil |

55 mil |

6 mil |

6 mil |

| 4 | 45 mil |

50 mil |

60 mil |

7 mil |

7 mil |

| 5 | 50 mil |

55 mil |

65 mil |

8 mil |

8 mil |

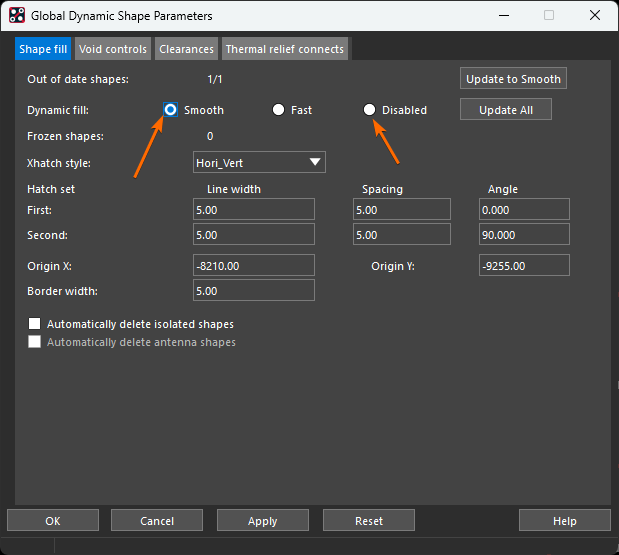

切换单位动态铺铜无法自动避让

当 Allegro 切换设计单位(Mils 或

Millimeter)之后,就会出现动态铺铜无法自动避让的问题。这是由于

Allegro 切换单位之后,动态铺铜变为

disabled 模式,此时需要鼠标点击 Allegro

顶部菜单栏上的

Shape -> Global Dynamic Params...,在打开的【Global

Dynamic Shape Parameters】话框当中,重新勾选具有自动避让功能的

smooth 模式:

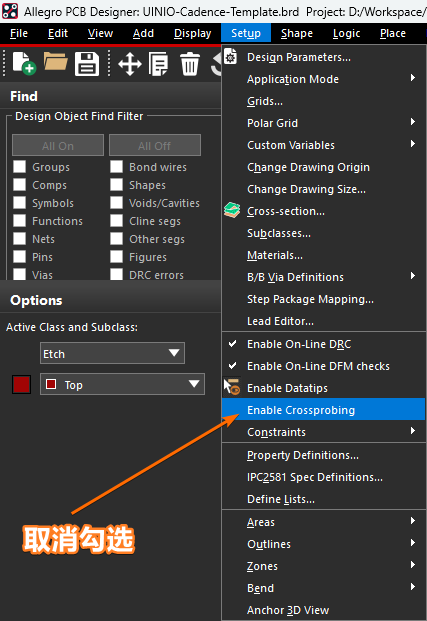

解除原理图与 PCB 的交互式布局

为了解决 Allegro 与 OrCAD

交互式布局时引发的运行缓慢问题,可以鼠标点击 Allegro

顶部菜单栏上的 Setup,取消 Enable Crossprobing

菜单项的勾选,从而临时解除原理图与 PCB

的交互式布局关系:

负片层的切割与网络指定

- 确认 PCB 板框的

Design Outline和Route Keepin区域是否绘制正确(两者相距至少0.5mm/20mil) - 在 Allegro 叠层管理器中设置好负片层;

- 执行 Allegro 菜单栏上的

Add -> Line命令,并且选择【Options】面板中的Class和Subclass分别为Anti Etch和相应的负片层; - 接下来在【Options】面板里的

Line width参数项当中,设置平面切割的宽度(即铺铜间距,通常设置为0.5mm/20mil或者1mm/40mil); - 根据负片层功能区域划分绘制好分隔线之后,点击

Allegro 菜单栏上的

Edit -> Split Plane -> Parameters…,勾选填充风格为Solid实心填充; - 接着鼠标选择 Allegro 菜单栏上的

Edit -> Split Plane -> Create,选择需要进行切割处理的负片层,并且指定其属于动态Dynamic还是静态Static类型的铺铜; - 按下【Create】按钮之后,窗口会自动聚焦到当前需要铺铜填充的区域,同时弹出【Select a net】对话框要求选择该区域所属的网络,选择并且确定之后,又会自动聚焦到下一个需要填充的区域;

过孔焊盘的创建步骤

- 【Drill】:钻孔参数设置(Finished diameter 表示钻孔直径)

- 【Drill Symbol】选项卡:设置显示在 Allegro 的 PCB

版图中的钻孔符号(即

Characters项设置的 3 个字母参数)。 - 【Design Layer】:规则焊盘

Regular Pad用于正片层、恒温焊盘Thermal Relief用于正片和负片层、负焊盘Anti Pad用于负片层(其中的Diameter参数表示的是过孔直径); - 【Mask Layer】:主要设置 阻焊层

SOLDERMASK_TOP/BOTTOM,从而达到过孔盖油的目的;

批量修改过孔类型

- 在 Allegro 绘制区展开鼠标右键菜单,切换

Application Mode -> General Edit; - Allegro 侧边栏的【Find】工作区里只勾选

Vias选项,然后选中需要执行修改的目标过孔; - 在 Allegro 绘制区展开鼠标右键菜单,选择

Replace padstack下的选项即可完成相应功能(其中Filter Instances可以用于指替换过孔);

加载外部 Skill 脚本

把需要加载的 Skill 脚本放置在任意目录下面,然后在下面的路径列表里找到

allegro.ilinit 文件,在其中加入

load("Skill文件名称") 代码即可:

C:\Cadence\Spb_data\pcbenv\allegro.ilinitC:\Cadence\SPB_17.4\share\pcb\etc\allegro.ilinit

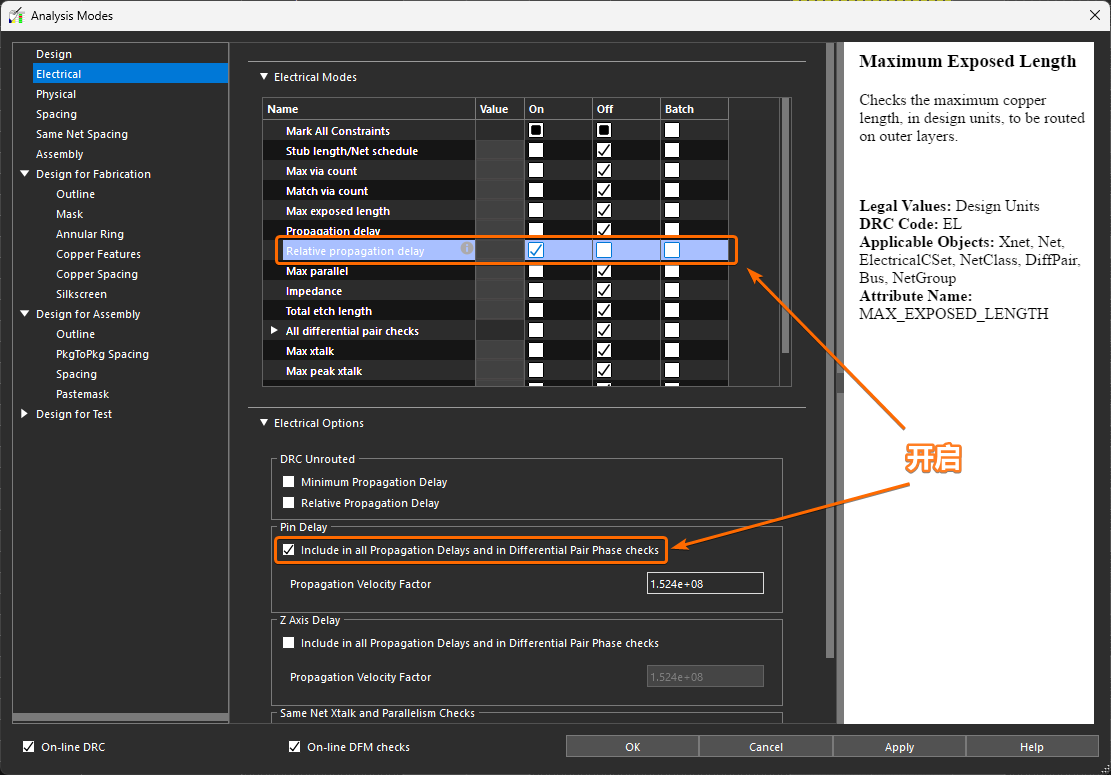

点对点相对等长布线

- 打开 Allegro 约束管理器当中的【Electrical -> Net -> Relative Propagation Delay】界面。

- 对需要进行等长布线的网络,在约束管理器当中建立

Net Group...或者Class...; - 鼠标依次选择约束管理器顶部菜单栏上的【Analyze -> Analysis Mode】或者直接按下快捷键【Ctrl + F9】;

- 分别勾选弹出对话框当中的

Relative propagation delay为【On】选项,以及界面底部的【Pin Delay】选项; - 分别设置该等长组的

Delta/Tolerance为0mil/5mil或者其它值,并且指定Target网络;

注意:

Delta:表示相对于Target长度的固定延迟。Tolerance:表示走线长度所允许的正负公差值。

Pin Pair 引脚对等长

- 打开 Allegro 约束管理器的【Electrical -> Net -> Relative Propagation Delay】界面,将需要进行等长处理的网络,添加到相同的 Class 或者 Net Group;

- 鼠标右键该 Class 或者 Net Group 下的每一个网络,然后依次点击

Create -> Pin Pair...创建 Pin Pair 的网络起始引脚First Pins和终点引脚Second Pins; - 然后鼠标全选上述步骤创建的所有 Pin Pair,然后右键依次点击

Create -> Match Group...创建等长组; - 分别设置该等长组的

Delta/Tolerance并且指定Target网络;

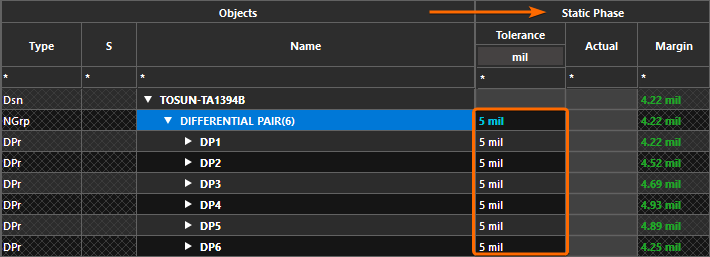

差分信号的对内相位等长

- 静态相位控制(Static Phase):用于控制差分对线之间的总长度偏差,但是在布线过程当中进行检查。

- 动态相位控制(Dynamic Phase):由于静态相位控制只能确定两条差分对线之间的总相位差,无法在布线过程中实时展示偏差情况,此时就需要使用到动态相位控制(也就是所谓的实时等长)。

通常情况下,差分信号对内等长需要小于或者等于

5mil,因而需要进行静态相位控制:

- 进入 Allegro 约束管理器的

Electrical -> Net -> Routing -> Differential Pair界面; - 设置表格当中的

Static Phase -> Tolerance列参数; - 返回 Allegro 的 PCB

绘制界面,并在【Find】面板上勾选

Nets,然后鼠标选择需要进行静态相位控制的差分网络,展开右键菜单勾选Single Trace Mode; - 最后依次勾选 Allegro 顶部菜单栏上的

Route -> Phase Tune,拖动目标差分线即可;

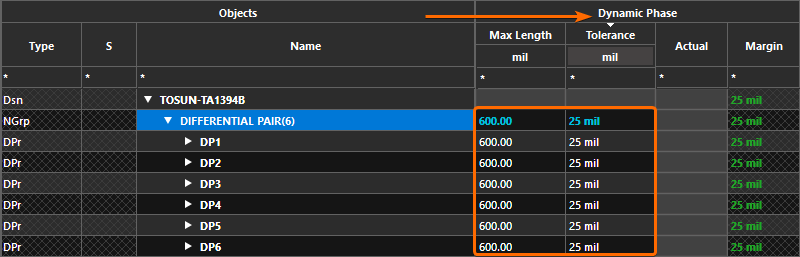

对于 5Gbit/s

以上速率的高速差分串行总线,需要考虑进行实时等长控制,即当走线偏差大于

25mil 时,必须在 600mil

的总布线长度之内进行补偿(使用反向拐角或者基于 3W

规则进行小波浪绕线来补偿):

- 进入 Allegro 约束管理器的

Electrical -> Net -> Routing -> Differential Pair界面; - 设置表格当中的

Dynamic Phase -> Tolerance列参数;

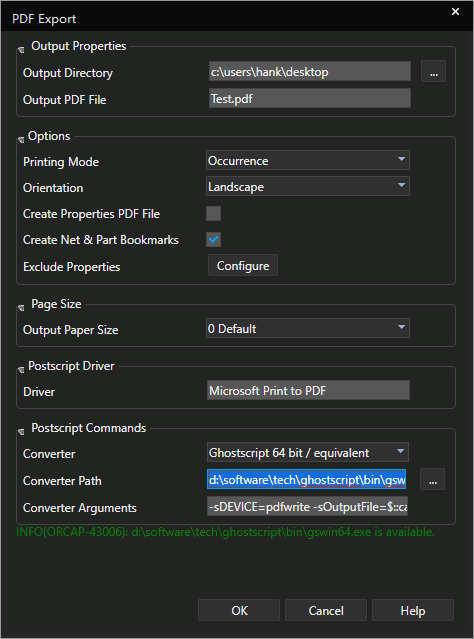

基于 Ghostscript 导出 PDF

基于 File -> Print... 方式导出的 PDF

原理图,存在无法对带有下划线的关键字进行搜索的问题,这里介绍一种使用开源

PDF 处理工具 Ghostscript 进行导出的办法:

- 前往 Ghostscript

官网下载

Ghostscript 10.06.0 for Windows (64 bit),并双击安装其到指定目录; - OrCAD 里选择当前需要导出的

.dsn原理图工程,然后鼠标依次点击File -> Export -> PDF; - 在弹出的【PDF Export】窗口,Postscript Driver

项填写为

Microsoft Print to PDF; - 除此之外,还需要分别设置

Converter项为Ghostscript 64 bit / equivalent,同时将Converter Path项指定为 Ghostscript 安装目录下的gswin64.exe文件; - 最后按下【OK】即可开始转换过程,稍等片刻即可在桌面或者指定路径获取到

.pdf格式的原理图文件;

Cadence SPB OrCAD/Allegro 设计技巧合集